Материалы по тегу: soc

|

21.04.2026 [08:49], Руслан Авдеев

Испанцы разрабатывают аппаратный «стоп-кран» для защиты от бэкдоров в зарубежных чипахНа фоне изменчивой геополитической обстановки и сопутствующих проблем Национальный центр суперкомпьютерных вычислений Барселоны (Barcelona Supercomputing Center, BSC) совместно с Политехническим университетом Каталонии (Politècnica de Catalunya, UPC) запустили проект Safe and Secure Technologies, сообщает EE Times. Он предназначен для разработки безопасных чипов для критической инфраструктуры и экстренных служб. Проект обеспечит разработки для сфер, в которых сбои в работе оборудования и угрозы безопасности могут иметь серьёзные последствия. В числе прочего это касается энергосетей, автомобильной промышленности, железнодорожного транспорта, телеком-сектора, гражданской обороны и др. ЕС стремится снизить зависимость от внешних технологий, поэтому Safe and Secure Technologies должен поспособствовать достижению технологического суверенитета. В компании заявляют, что уязвимость часто заключается не в доступности оборудования, а в его происхождении. Проблема в том, что Европа в контексте чипов для критически важных систем во многом зависит от технологий из США, Тайваня и Юго-Восточной Азии в целом. Предполагается, что при определённых условиях сторонние игроки могут, например, использовать недокументированный бэкдор для полного отключения энергосистемы и др.

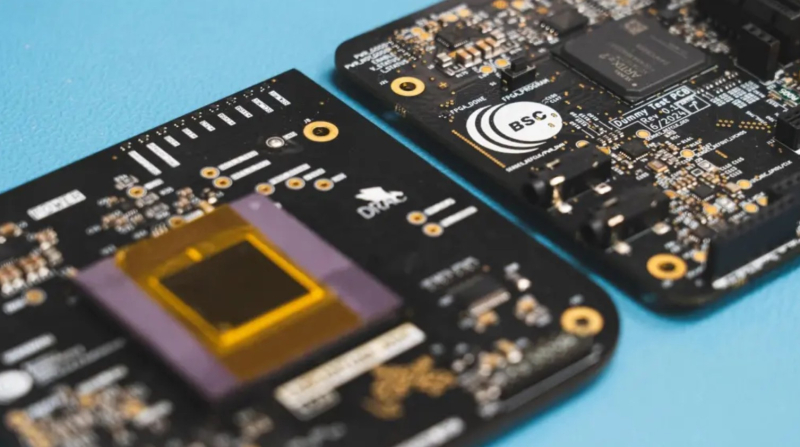

Источник изображения: Barcelona Supercomputer Center Акцент в проекте сделан не на создании собственных уникальных решений, а на прозрачности, позволяющей полностью проверить безопасность продуктов. Основным аппаратным компонентом проекта станет т.н. «остров безопасности» (Safety Island), созданный на основе наработок европейских программ De-RISC, SELENE, ISOLDE и FRACTAL — интегрированный модуль обеспечения безопасности. Этот компонент будет устанавливаться в непосредственной близости от процессора и гарантирует, что устройство будет работать в соответствии со спецификации, необходимыми пользователю. Фактически модуль контролирует работу основного процессора, отслеживает выполнение им задач в режиме реального времени и распределение ресурсов. Если эти условия не соблюдаются, модуль способен или сам принять меры, или инициировать прерывание, чтобы ПО или операционная система отреагировали на него в соответствии с пользовательскими запросами. Заявлено, что разработанное «железо» может выйти из строят только в исключительных обстоятельствах. В этому случае оно распознаёт ситуацию и контролируемым образом прерывает исполнение до того, как остальная система получит ошибочные инструкции.

Источник изображения: Barcelona Supercomputer Center Разработка Safe and Secure Technologies ориентирована в первую очередь на интеграцию с продуктами на базе RISC-V, но в целом «ядро», предназначенное для размещения в хост-процессоре, можно интегрировать и с чипами Intel, Arm и AMD. Учитывая будущие нормативные требования и требования к безопасности продуктов, компания намерена поддерживать передовые стандарты криптографии. Строго говоря, продукт не является «криптографическим чипом как таковым», поскольку в его задачи входит контроль над функциями безопасности, но в будущем по запросу клиентов можно добавить даже поддержку «квантовой криптографии». У компании не будет собственных производственных мощностей, основное внимание она будет уделять проектированию, а собственно выпуск поручат контрактным производителям. Сейчас проект работает над привлечением капитала, чтобы поменьше зависеть от государственных субсидий. Хотя возможности для государственного финансирования открыты, они не являются основным драйвером разработок. Переговоры с инвесторами продолжаются, ожидается, что в конечном итоге численность персонала составит несколько десятков человек. Выход на рынок будет зависеть от капитализации, начать работы планируется через 6-12 месяцев, после чего возможно значительное ускорение. Safe and Secure Technologies — уже пятнадцатый проект, «отпочковавшийся» от BSC. Ранее коммерческие предприятия центра уже привлекли €44 млн частного капитала и наняли более 600 специалистов. В феврале сообщалось, что BSC уже активно участвует в гонке за обретением Европой технологического суверенитета. Первый европейский суверенный RISC-V-процессор Cinco Ranch изготовлен по техпроцессу Intel 3. В этом приняла непосредственное участие Лаборатория суперкомпьютерных вычислений (BZL) центра BSC-CNS, а в апреле появилась информация, что процессор готов к началу массового производства.

14.03.2026 [10:16], Сергей Карасёв

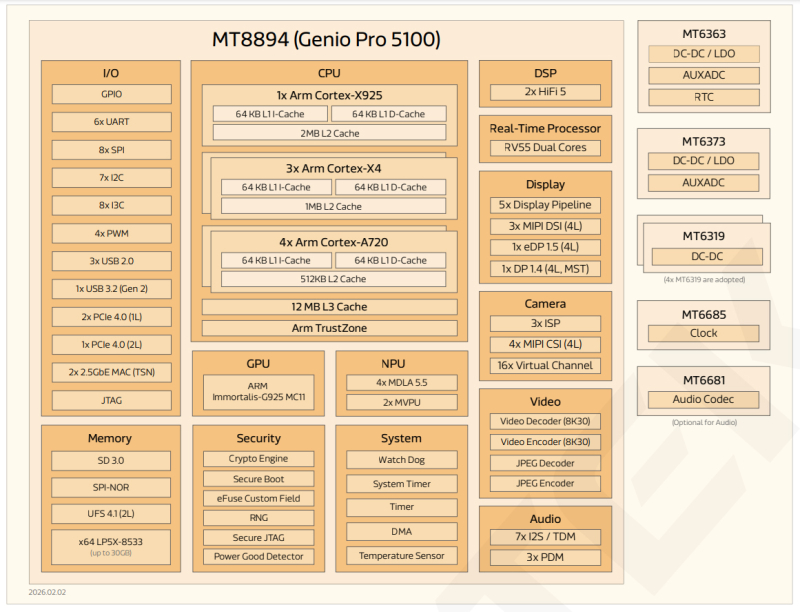

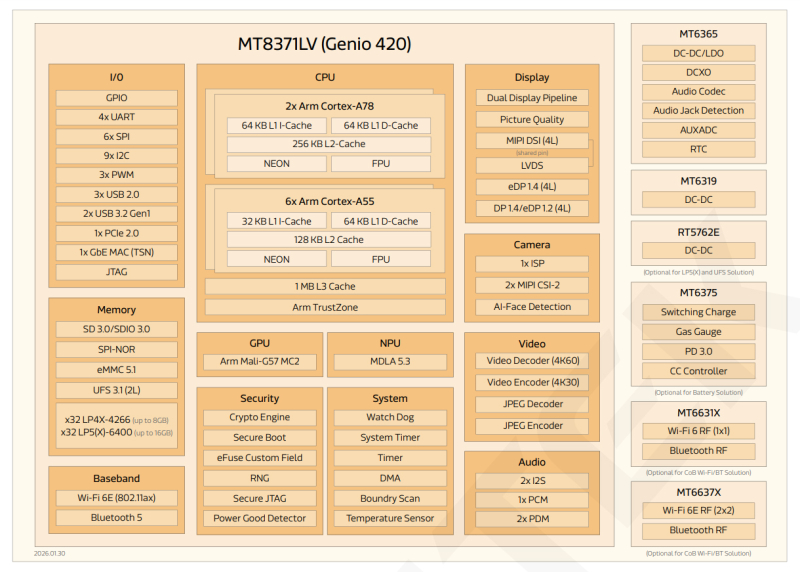

MediaTek представила чипы Genio Pro 5100 и Genio 420 для AIoT-приложенийКомпания MediaTek представила процессоры Genio Pro 5100 и Genio 420 с архитектурой Arm для AIoT-приложений и встраиваемых систем. Первый из названных чипов подходит, в частности, для автономных мобильных роботов, дронов, периферийного оборудования и автомобильных платформ, второй — для устройств умного дома, интерактивных дисплеев и пр. Изделие Genio Pro 5100 изготавливается по 3-нм технологии. Оно содержит восемь вычислительных ядер в конфигурации 1 × Arm Cortex-X925, 3 × Arm Cortex-X4 и 4 × Arm Cortex-A720. Присутствуют графический блок Arm Immortalis-G925 MC11 с поддержкой OpenGL, Vulkan и OpenCL, а также нейропроцессорный узел (NPU) с ИИ-производительностью более 50 TOPS. Модуль VPU обеспечивает возможность кодирования материалов H.264 и H.265 (до 8K30) и декодирования H.264, H.265, AV1 и VP9 (до 8K30). Реализована поддержка оперативной памяти LPDDR5x-8533 (до 30 Гбайт), а также флеш-памяти UFS 4.1, SD 3.0 и SPI-NOR. Допускается вывод изображения одновременно на три дисплея формата 4Kp60 через интерфейсы eDP 1.5 (4 линии), DisplayPort 1.4 (MST) и 3 × MIPI DSI (4 линии). Благодаря четырём интерфейсам MIPI-CSI (4 линии) возможно использование до 16 камер (1080p30). Среди прочего упомянута поддержка 2 × 2.5GbE, Wi-Fi 7 и Bluetooth 5.4 (через внешний модуль), 1 × PCIe 4.0 (2 линии) и 2 × PCIe 4.0 (1 линия), 6 × UART, 7 × I2C, 8 × I3C, 4 × PWM, 7 × I2S/TDM, 3 × PDM, 1 × USB 3.2 Gen2 (10 Гбит/с), 2 × USB 2.0 (Host/Device) и 1 × USB 2.0 (Host). Изделие выполнено в корпусе ETFC TFBGA с размерами 15,9 × 16,6 мм. Диапазон рабочих температур простирается от -40 до +105 °C. Вторая новинка, Genio 420, производится по 6-нм технологии. Процессор объединяет восемь ядер (2 × Arm Cortex-A78 с тактовой частотой 1,8 ГГц и 6 × Arm Cortex-A55 с частотой 1,6 ГГц) и графический ускоритель Arm Mali-G57 MC2. Модуль MediaTek NPU восьмого поколения обеспечивает ИИ-производительность на уровне 6,1 TOPS. Блок VPU поддерживает кодирование материалов H.264/H.265 (до 4Kp30) и декодирование H.264/H.265/VP9 (до 4Kp60) и MPEG4/VP8 (до 1080p60). Чип позволяет использовать оперативную память LPDDR4X-4266 (до 8 Гбайт) и LPDDR5/LPDDR5X-6400 (до 16 Гбайт), а также флеш-память UFS 3.1 (2 линии), eMMC 5.1, SD 3.0 / SDIO 3.0, SPI-NOR. Возможен вывод изображения на монитор 4Kp60 или два дисплея 2.5Kp60 через интерфейсы eDP, DP, LVDS и MIPI-DSI. Допускается использование до шести камер 1080p30 через 2 × MIPI-CSI. Прочие характеристики процессора таковы: контроллер 1GbE, опциональные адаптеры Wi-Fi 6 (1×1) + Bluetooth 5.3 на базе MT6631X или Wi-Fi 6E (2×2) + Bluetooth 5.3 на основе MT6637X, 1 × PCIe 2.0 (1L, RC, WoWLan), 4 × UART, 9 × I2C, 6 × SPI Master, 3 × PWM, GPIO, JTAG, 3 × USB 2.0, 1 × USB 3.0 (5 Гбит/с; Host), 1 × USB 3.0 (Host/Device). Чип выполнен в корпусе VFBGA с размерами 13,8 × 11,8 × 0,9 мм. Диапазон рабочих температур — от -20 до +95 °C. Процессоры поддерживают такие средства обеспечения безопасности, как Arm TrustZone, Security Boot (RSA4096), Crypto Engine и RNG. Говорится о совместимости с различными вариантами Linux, включая Yocto и Ubuntu.

02.03.2026 [08:59], Владимир Мироненко

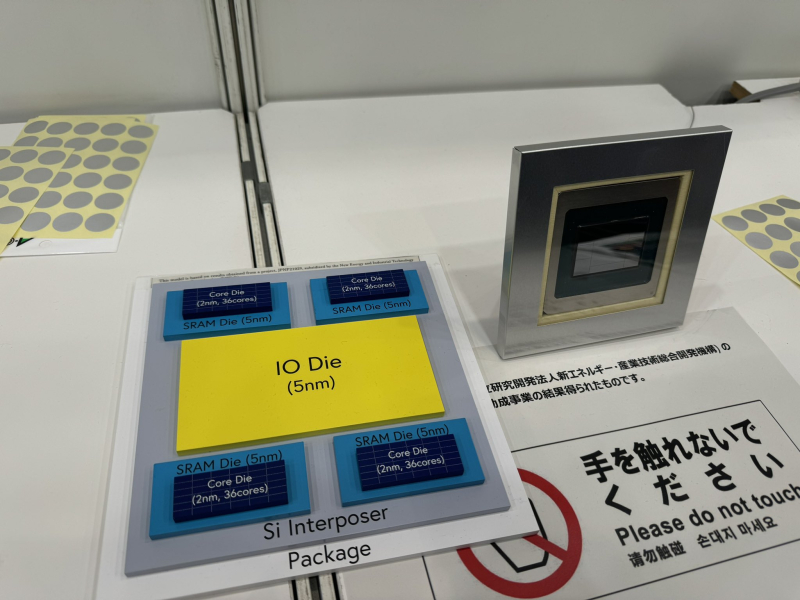

Fujitsu похвасталась, что её 2-нм процессоры MONAKA получат продвинутую упаковку Broadcom 3.5D XDSiPBroadcom объявила о начале поставок первой в отрасли 2-нм специализированной SoC, построенной на платформе 3.5D eXtreme Dimension System in Package (XDSiP). Модульная многомерная платформа с многослойной компоновкой чиплетов, 3.5D XDSiP, которая используется в чипе Fujitsu MONAKA, сочетает в себе 2.5D-упаковку и 3D-интеграцию с использованием технологии гибридного соединения между чиплетами (Face-to-Face, F2F), значительно повышающего пропускную способность. Сообщается, что технология 3.5D XDSiP станет основой XPU следующего поколения. С её помощью компании в сфере ИИ могут создавать самые передовые XPU с «беспрецедентной плотностью сигнала, превосходной энергоэффективностью и низкой задержкой», позволяющие удовлетворить вычислительные потребности ИИ-кластеров гигаваттного масштаба. Платформа Broadcom XDSiP позволяет масштабировать вычислительные ресурсы, память и сетевые интерфейсы независимо друг от друга в компактном форм-факторе, обеспечивая энергоэффективные вычисления с высокой производительностью, говорит компания. «Мы гордимся тем, что представили первый специализированный SoC на базе 3.5D-упаковки для Fujitsu», — сказал Фрэнк Остоич (Frank Ostojic), старший вице-президент и генеральный директор подразделения ASIC-продуктов Broadcom. Он отметил, что с момента внедрения технологии 3.5D XDSiP в 2024 году компания Broadcom расширила возможности своей 3.5D-платформы, чтобы поддерживать XPU для более широкой клиентской базы, поставки которых начнутся во II половине 2026 года. Как отметил ресурс The Register, Fujitsu стала одной из первых компаний-разработчиков чипов, публично признавших использование этой технологии Broadcom. Обычно клиенты Broadcom не стремятся предать огласке, какие IP-блоки они лицензируют, а какие создают сами. Например, всем известно, что Google тесно сотрудничает с Broadcom в разработке TPU, но не всегда ясно, где заканчивается вклад Google и начинается работа Broadcom. «Мы работаем над этой технологией почти пять лет, — рассказал The Register Хариш Бхарадвадж (Harish Bharadwaj), вице-президент подразделения ASIC-продуктов Broadcom. — Мы отгрузили образцы на этой неделе для Fujitsu, и в своё время многие другие наши клиенты внедрили эту технологию для своих [решений] следующих поколений». Разрабатываемый Fujitsu чип MONAKA включает четыре 2-нм вычислительных чиплета, каждый — с 36 ядрами Armv9-A, расположенные поверх четырёх SRAM-чиплетов, изготовленных по 5-нм техпроцессу TSMC. Эти стеки объединяются с центральным I/O-чиплетом, который обслуживает 12 каналов DDR5 и линии PCIe 6.0/CXL 3.0, через кремниевую подложку-интерпозер. Кроме того, новинки получат поддержку NVIDIA NVLink. По словам Бхарадваджа, Fujitsu стала одной из первых компаний из числа внедривших технологию 3.5D XDSiP, но MONAKA является лишь одним из примерно полудюжины разрабатываемых проектов. Хотя MONAKA — это платформа для процессоров, примерно 80 % успешных проектов Broadcom с использованием XDSiP приходится на XPU с HBM, отметил он. В 2024 году сообщалось о поддержке платформой решений с 12 стеками HBM. В компании рассказали The Register, что сейчас разрабатываются проекты с более чем 12 стеками.

10.02.2026 [12:09], Сергей Карасёв

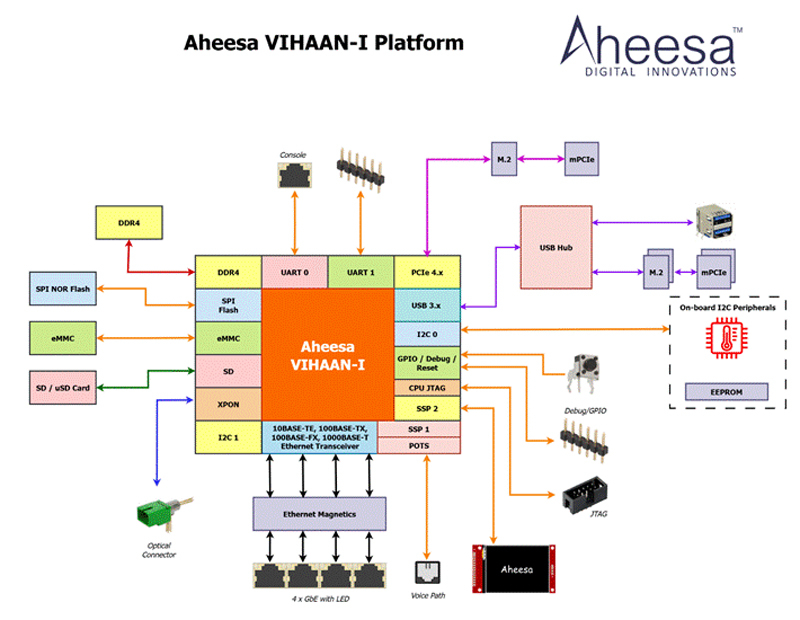

Стартап Aheesa создал первый в Индии чип RISC-V для PON-сетейИндийский безфабричный стартап Aheesa Digital Innovations, по сообщению EE Times, завершил разработку первой в стране «системы на чипе» (SoC) с архитектурой RISC-V, ориентированной на волоконно-оптические сети широкополосного доступа в интернет. Изделие получило обозначение VIHAAN-I. Новинка предназначена для инфраструктур GPON (Gigabit Passive Optical Network) и EPON (Ethernet Passive Optical Network). Решение объединяет на одном кристалле вычислительные ресурсы, средства управления и широкополосного доступа. VIHAAN-I является частью платформы Aheesa Seshnag. В состав новинки входит RISC-V-ядро C-DAC Vega. Реализована поддержка памяти DDR4 и SPI NOR, флеш-карт SD и microSD, а также интерфейса xPON. Заявлена совместимость с Ethernet-стандартами 10BASE-TE, 100BASE-TX, 100BASE-FX и 1000BASE-T. Изделие объединяет многопортовый гигабитный Ethernet и прямое оптоволоконное соединение. Среди прочего упомянуты интерфейсы USB и PCIe (четыре линии) с возможностью использование модулей M.2 и mini-PCIe. Кроме того, предусмотрена интегрированная поддержка голосовой связи. SoC будет производиться на предприятии UMC с применением 28-нм технологии.

Источник изображения: Aheesa Digital Innovations / EE Times Выбор архитектуры RISC-V, как заявляет Aheesa Digital Innovations, обусловлен прежде всего соображениями безопасности. Поддерживаются стандартные сетевые функции, такие как коммутация Ethernet, маршрутизация, службы межсетевого экрана, VPN, протокол динамической конфигурации хоста и пр. Примерно на 60% решение состоит из стандартных лицензированных компонентов, таких как контроллеры памяти и интерфейсные блоки. Заявлена совместимость с последними версиями ядра Linux. Aheesa Digital Innovations основана в 2021 году Шридхараном Мани (Sridharan Mani), который занимает пост генерального директора. Компания получила поддержку в рамках индийской программы стимулирования разработок. Стартап сотрудничает с рядом государственных учреждений, включая Министерство электроники и информационных технологий (MEITy) и Центр развития передовых вычислительных технологий (C-DAC). Aheesa Digital Innovations намерена предлагать свои решения OEM- и ODM-производителям, системным интеграторам и дистрибьюторам, которые поставляют устройства телекоммуникационным операторам. В дальнейшем стартап планирует активно развивать семейство собственных SoC. В частности, готовятся решения с поддержкой 10GbE и Wi-Fi 7.

28.12.2025 [15:42], Владимир Мироненко

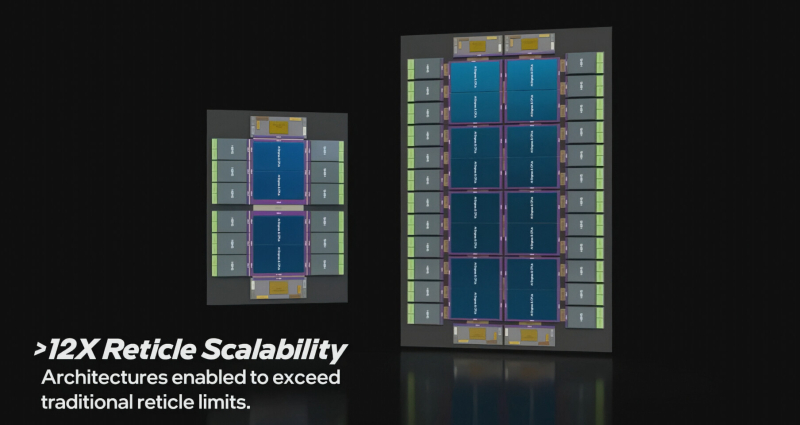

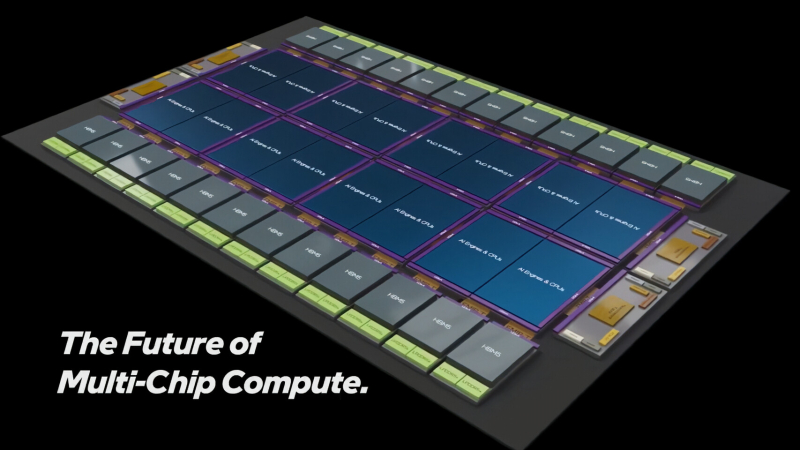

16 вычислительных тайлов и 24 стека HBM: Intel продемонстрировала свои возможности для создания будущих чиповIntel Foundry опубликовала видео с демонстрацией своих передовых решений в области упаковки микросхем с использованием технологических процессов 18A/14A, технологий Foveros 3D и EMIB-T. В видео представлены концептуальные и масштабируемые конструкции с возможностью размещения до 16 вычислительных блоков, 24 стеков HBM и многое другое. Как отметил ресурс WCCFTech, видеоролик демонстрирует, что ждёт клиентов Intel, стремящихся использовать её технологии при создании будущих чипов. Эти технологии будут устанавливать стандарты для чипов следующего поколения для HPC, ИИ, ЦОД и многого другого. Передовые решения в области упаковки также усилят позиции Intel в конкуренции с TSMC, которая представили решение CoWoS, обеспечивающее 9,5-кратное превышение размеров стандартного фотошаблона (830 мм²), использующее технологический процесс A16 и более 12 стеков HBM4E (CoWoS-L). Согласно видео, технологии Intel Foveros 3D и межкристального соединения EMIB-T позволяют объединить до 16 вычислительных кристаллов в паре с 24 стеками HBM5 в одном корпусе. При этом используются 18A-процессы Intel, включая 18A-P и 18A-PT, и 14A-процессы, которые компания готовит к массовому производству, в том числе для внешних заказчиков. В опубликованном видеоролике Intel демонстрирует два передовых решения для корпусирования микросхем. Одна микросхема включает четыре вычислительных блока и 12 модулей HBM, а вторая — 16 вычислительных блоков и 24 модуля HBM. Также у более крупной размещено в одном корпусе вдвое больше контроллеров LPDDR5X, до 48, что значительно увеличивает плотность памяти для ИИ-нагрузок и ЦОД. Для создания микросхем используется технология послойного объединения кристаллов, при которой базовые кристаллы, изготовленные с использованием процесса 18A-PT, используют подачу питания с обратной стороны (PowerVia) и включают SRAM-банки. На базовый тайл затем устанавливается основной вычислительный тайл, который может включать в себя ИИ-движки, CPU или другие IP-блоки. Они изготавливаются по технологическим процессам Intel 14A или 14A-E, используют транзисторы RibbonFET второго поколения и технологию PowerDirect, и соединяются с базовым тайлом с помощью технологии Foveros Direct 3D, обеспечивающей вертикальное размещение компонентов, образуя 3D-стек. Затем несколько чиплетов соединяются и дополнительно взаимодействуют с памятью с помощью технологии упаковки EMIB-T. Верхний тайл использует 24 модуля HBM, которые могут поддерживать как существующие стандарты HBM, такие как HBM3/HBM3E, так и будущие, такие как HBM4/HBM4E или HBM5. При этом активно используется UCIe. Теперь дело за практической реализацией замыслов. Компания возвращается на рынок с ИИ-ускорителем Jaguar Shores и GPU Crescent Island для ИИ-инференса, но всё зависит от сделок со сторонними поставщиками.

19.12.2025 [13:24], Сергей Карасёв

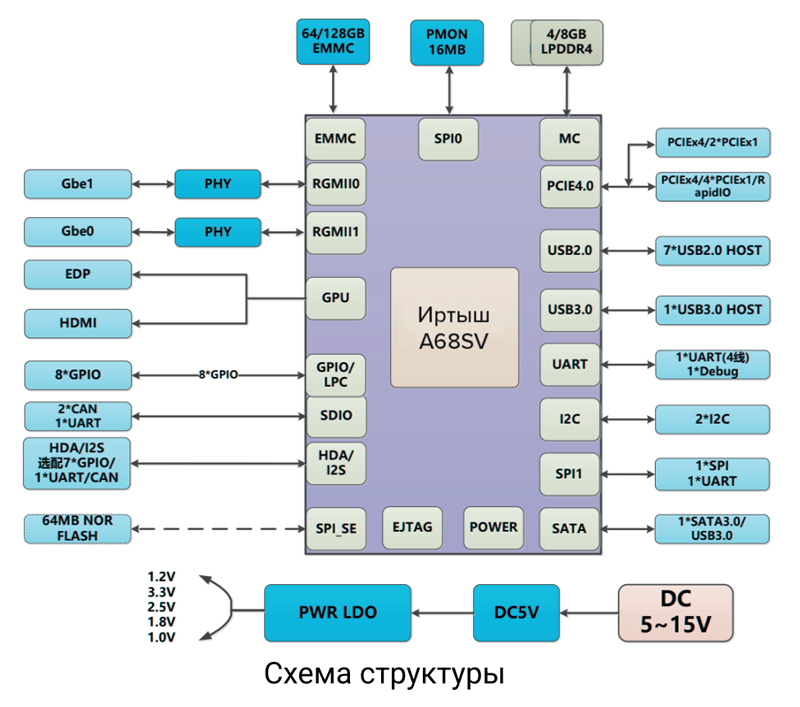

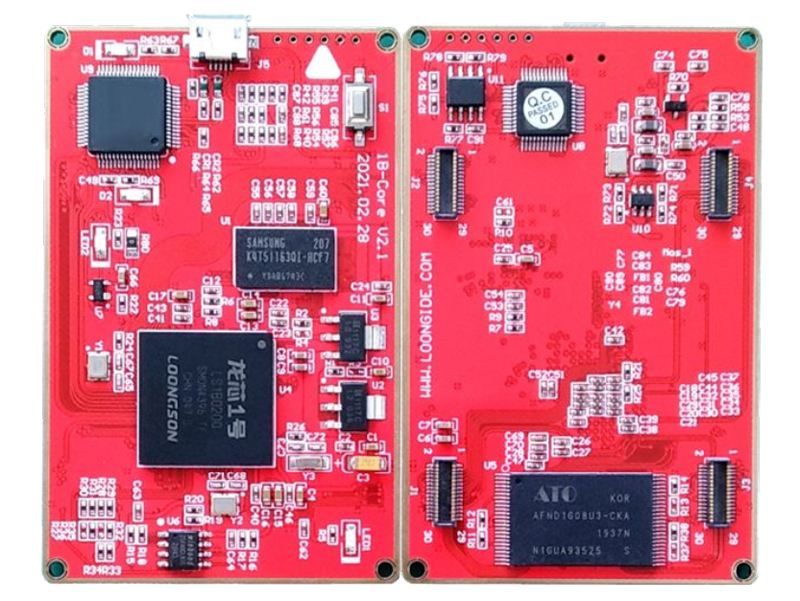

«Трамплин Электроникс» представила российскую SoC «Иртыш A68SV» с китайской архитектурой LoongArchРоссийская компания «Трамплин Электроникс» представила отечественную «систему на кристалле» (SoC) под названием «Иртыш A68SV». Изделие может применяться для создания систем промышленного управления, коммуникационного оборудования, устройств интернета вещей (IoT) и пр. Новинка выполнена на китайской архитектуре LoongArch (LA364). Задействованы два вычислительных ядра с максимальной тактовой частотой 2 ГГц. Каждое ядро содержит по 64 Кбайт кеша инструкций и данных L1 и 2 Мбайт кеша L2. Поддерживается оперативная память DDR4-2400 ECC. Упомянуты интерфейсы USB 3.0/2.0, HDMI, DVO, Gnet, GMAC, SDIO, EMMC, САМ, PCIe 3.0 и SATA 3.0. Типовое энергопотребление находится в диапазоне от 3 до 9 Вт. Кроме того, «Трамплин Электроникс» анонсировала плату для разработчиков Devboard на базе архитектуры LoongArch LA364E. Используются восемь ядер с частотой до 2 ГГц и поддержкой 128-битных операций с плавающей точкой. Объём памяти DDR4 может достигать 64 Гбайт. Имеется интегрированное графическое ядро с поддержкой OpenGL 3.3, OpenGL ES 3.1 и OpenCL 1.1. Возможна обработка видео в формате 4K с частотой до 60 к/с. В число доступных интерфейсов входят PCIe 3.0, SATA 3.0, USB 3.1, RapidIO 2.0, USB 2.0, GMAC, SDIO, eMMC, CANFD и аудио.

Источник изображений: «Трамплин Электроникс» Плата Devboard соответствует стандарту COM Express. Среди её сфер использования названы контроллеры для промышленной автоматизации и IoT-оборудования, бортовые вычислители для транспортных средств и беспилотных летательных аппаратов, измерительная техника и др. Плата позволит упростить знакомство с возможностями архитектуры LoongArch.  Как отмечается, на текущий момент LoongArch является третьей по популярности CPU-архитектурой в мире после x86 и Arm. LoongArch поддерживается крупными open source проектами, включая ядро Linux, GCC, LLVM. Эта архитектура не подвержена первичным и вторичным санкциям, а поэтому в сформировавшейся геополитической обстановке является единственной альтернативой популярным зарубежным решениям, которую возможно произвести в «кремнии» для использования в России.

16.12.2025 [17:50], Владимир Мироненко

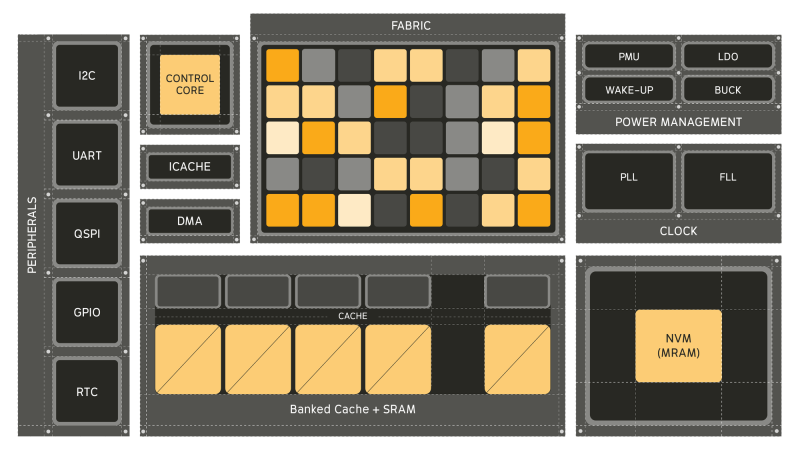

Универсальный ИИ-процессор Electron E1 в 100 раз энергоэффективнее традиционных CPUСтартап из Питтсбурга (Pittsburgh) Efficient Computer выпустил оценочный набор универсального процессора Electron E1 (EVK). Как сообщает компания, Electron E1 представляет собой настоящую альтернативу чипам с использованием традиционной архитектуры фон Неймана, способную обеспечить значительно более высокую энергоэффективность, в 100 раз превышающую показатели обычных маломощных процессоров, таких как Arm Cortex-M33 и Cortex-M85. Electron E1 предназначен для выполнения сложных задач обработки сигналов и инференса. Он основан на т.н. Efficient Fabric, разработанной компанией запатентованной архитектуре пространственного потока данных, которая позволяет снизить «чрезмерное» энергопотребление, связанное с перемещением данных между памятью и вычислительными ядрами, характерное для традиционных систем фон Неймана. При этом «разработчики по-прежнему получают привычный опыт программирования, но с существенно более высокой энергоэффективностью». Генеральный директор Efficient Брэндон Лючия (Brandon Lucia) в интервью EE Times заявил, что предыдущие попытки отойти от подхода фон Неймана так и не были полностью реализованы: «Были мимолётные альтернативы, которые появлялись и исчезали». Он отметил, что одним из ограничений во многих альтернативах был отказ от универсальности вычислений: «Это действительно критически важно». Нечто похожее предлагает и NextSilicon Maverick. Процессор включает 128 Кбайт сверхэкономичной кеш-памяти, 3 Мбайт SRAM и 4 Мбайт энергонезависимой MRAM, а его производительность может достигать 21,6 GOPS (млрд операций в секунду) при 200 МГц в высоковольтном режиме и 5,4 GOPS при 50 МГц в низковольтном режиме. Архитектура Fabric коренным образом переосмысливает способ выполнения вычислений, уменьшая необходимость в перераспределении данных между памятью и процессорами, говорит Лючия. Это достигается за счёт пространственного отображения операций по сетке вычислительных элементов, каждый из которых активируется только тогда, когда доступны его входные данные в отличие от непрерывного цикла инструкций и косвенной адресации данных, которые доминируют в традиционных конвейерах CPU. Лючия отметил, что универсальный процессор важен для ИИ-технологий, поскольку он представляет собой нечто гораздо большее, чем просто алгоритмы в физическом мире — он обеспечивает, в том числе, интеграцию данных с датчиков, цифровую обработку сигналов, шифрование и преобразование: «Если ваша архитектура специализируется только на одном типе вычислений, все остальные функции остаются невостребованными». По словам главы Efficient, Electron E1 разработан для поддержки всего кода, необходимого для работы приложения, что делает его идеальным для периферийных вычислений, встроенных систем и ИИ-приложений: «Разработчики могут использовать уже имеющийся у них код». Лючия отметил, что процессор лучше всего подходит для устройств, требующих длительного времени автономной работы, а также условий ограниченного энергопотребления, например, для использования в дронах и промышленных датчиках. Чип уже используется в устройствах партнёра Efficient, компании BrightAI, позволяя обрабатывать ИИ-нагрузки в реальном времени на периферии и снижая потребность в энергоемких облачных вычислениях для таких задач, как обработка сигналов и инференс. Лючия сообщил, что компания видит большие перспективы для использования чипа в робототехнике, автомобилестроении, космосе и оборонных приложениях, которые имеют ограничения по размерам и мощности. Что касается E1 EVK, то он, по словам компании, разработан для того, чтобы максимально упростить изучение потенциала нового процессора. Независимо от того, разрабатываете ли вы новое ПО, проводите анализ энергопотребления или портируете существующее ПО, EVK предоставляет:

В случае отсутствия оборудования можно использовать решение Electron E1 Cloud EVK, которое предоставляет размещённую среду со всеми возможностями физической платы. Как физический EVK, так и облачный EVK доступны в рамках программы раннего доступа Efficient Computer.

16.11.2025 [12:35], Сергей Карасёв

Qualcomm представила чипы Dragonwing IQ-X для индустриальных Windows-компьютеровКомпания Qualcomm анонсировала новые SoC семейства Dragonwing IQ-X — изделия IQ-X5181 и IQ-X7181, ориентированные на индустриальный сектор. Чипы предназначены для построения промышленных Windows-компьютеров, систем автоматизации, робототехнических платформ, медицинского оборудования и пр. Решение IQ-X5181 объединяет восемь кастомизированных ядер Qualcomm Oryon (Armv8) с тактовой частотой до 3,4 ГГц, модификация IQ-X7181 — двенадцать. В состав SoC входит графический ускоритель Qualcomm Adreno с частотой соответственно 1,1 и 1,25 ГГц. Младшая версия способна справляться с декодированием видеоматериалов 4Kp60 VP9/AV1 и кодированием 4Kp30 AV1, старшая — 4K120 VP9/AV1 и 4Kp60 AV1. Чипы обеспечивают ИИ-производительность до 45 TOPS с учётом блоков CPU, GPU и Hexagon NPU.

Источник изображения: Qualcomm Возможно использование до 64 Гбайт оперативной памяти LPDDR5X-4200, флеш-накопителей UFS 4.0 и карт SD/MMC (SD 3.0). Реализованы интерфейсы eDP (eDP1.4b) с поддержкой разрешения до 4096 × 2160 пикселей при 60 Гц и DisplayPort v1.4a (через USB) с поддержкой разрешения до 5120 × 2880 точек при 60 Гц. Изделие IQ-X5121 располагает двумя интерфейсами камер CSI на четыре линии каждый, IQ-X7181 — четырьмя. Для обеих новинок заявлена поддержка 2 × USB 3.1, 3 × USB 4.0 Type-C (DisplayPort v1.4a Alt Mode), 6 × eUSB 2.0 и 221 × GPIO (UART, SPI, I3C, I2C via QUP). В случае IQ-X5181 реализованы интерфейсы 2 × PCIe 4.0 х4 и 2 × PCIe 3.0 х2, в случае IQ-X7181 — PCIe 4.0 х8, PCIe 4.0 х4 и 2 × PCIe 3.0 х2. Кроме того, говорится о поддержке Ethernet (чип-компаньон QPS615), Wi-Fi и Bluetooth (посредством модуля M.2 PCIe), Wi-Fi 7 / Wi-Fi 6E (через WCN785/WCN6856), а также 5G (модем Snapdragon X65). Изделия выполнены в корпусе 1747-ball BGM с размерами 58 × 58 мм с максимальной толщиной 3 мм. Диапазон рабочих температур простирается от -40 до +105 °C. Говорится о совместимости с Windows 10/11 IoT Enterprise LTSC, Qt, CODESYS, EtherCAT и пр. Гарантирована доступность чипов в течение более чем 10 лет.

27.10.2025 [11:16], Сергей Карасёв

Axelera AI представила ИИ-чип Europa с производительностью 629 TOPSНидерландский стартап Axelera AI анонсировал ИИ-ускоритель (AIPU) под названием Europa, предназначенный для таких задач, как генеративные сервисы и приложения компьютерного зрения. По заявлениям разработчиков, чип может использоваться в оборудовании разного класса — от периферийных устройств до корпоративных серверов. В состав Europa AIPU входят восемь «ядер ИИ второго поколения», которые используют векторные движки и технологию цифровых вычислений в оперативной памяти (D-IMC), разработанные специалистами Axelera. Заявленная ИИ-производительность достигает 629 TOPS на операциях INT8. Кроме того, чип содержит 16 специализированных векторных ядер с архитектурой RISC-V, сгруппированных в два кластера: они предназначены для операций пред- и постобработки, не связанных с ИИ. Пиковая производительность блока RISC-V достигает 4915 GOPS (млрд операций в секунду). Интегрированный декодер H.264/H.265 ускоряет выполнение медиазадач. Процессор располагает 256-бит интерфейсом памяти LPDDR5 с пропускной способностью 200 Гбайт/с и 128 Мбайт памяти L2 SRAM. Новинка будет предлагаться в различных форм-факторах, включая компактное исполнение с размерами 35 × 35 мм и карты расширения PCIe 4.0 х4 в различных конфигурациях, в частности, с одним чипом и 16 Гбайт памяти, а также с четырьмя чипами и 256 Гбайт памяти. Разработчикам предоставляет комплект Voyager SDK, который позволяет полностью раскрыть потенциал процессора. В целом, как утверждается, новинка обеспечивает в 3–5 раз более высокую производительность в расчёте на 1 Вт и $1 по сравнению с ведущими отраслевыми решениями в той же категории. Поставки Europa AIPU и PCIe-карт начнутся в I половине 2026 года.

19.07.2025 [13:39], Сергей Карасёв

Rockchip представила 10-ядерный Arm-процессор RK3668 с ИИ-модулемКомпания Rockchip, как сообщает ресурс CNX Software, процессор RK3668 на архитектуре Arm, предназначенный для создания одноплатных компьютеров и других устройств с ИИ-функциями. Изделие насчитывает 10 вычислительных ядер в конфигурации 4 × Arm Cortex-A730 и 6 × Arm Cortex-A530 (Armv9.3). Причём на сегодняшний день эти ядра официально не представлены. В состав чипа входят графический процессор Arm Magni с производительностью до 1–1,5 Тфлопс и блок VPU с возможностью декодирования материалов в формате 8K (60 к/с). Новинка располагает интегрированным нейропроцессорным модулем (NPU) с быстродействием до 16 TOPS для ускорения ИИ-операций. Процессор изображений (ISP) с ИИ-функциями поддерживает работу с видео 8K (30 к/с). Реализованы четыре канала оперативной памяти LPDDR5/5x/6 с пропускной способностью до 100 Гбайт/с. Возможно использование флеш-накопителей UFS 4.0. Поддерживаются интерфейсы HDMI 2.1 (до 8K / 60 к/с), MIPI DSI, PCIe, UCIe. Производственные нормы — 5–6 нм. Кроме того, Rockchip раскрыла дополнительную информацию о чипе RK3688, первые упоминания которого появились в октябре 2024 года. Это изделие объединяет 12 вычислительных ядер в конфигурации 8 × Arm Cortex-A730 и 4 × Arm Cortex-A530. Пропускная способность памяти LPDDR6 достигает 200 Гбайт/с. Возможно декодирование видеоматериалов 16Kp30 и кодирование 8Kp60. Производительность встроенного NPU-блока повышена до 32 TOPS. Этот процессор будет изготавливаться по технологии 4–5 нм. Одной из первых компаний, которая возьмёт на вооружение новые чипы, станет Radxa: она, в частности, готовит одноплатный компьютер Rock 6 на основе RK3668. |

|