Материалы по тегу: cpu

|

18.09.2019 [19:50], Андрей Созинов

AMD представила EPYC 7H12: самый быстрый процессор семейства RomeСегодня в Риме компания AMD провела европейскую презентацию процессоров EPYC Rome (символично, не правда ли?), на которой неожиданно представила совершенно новый процессор — EPYC 7H12. Новинка отличается не только своим нестандартным названием, но и характеристиками, которые делают её самым мощным серверным процессором AMD на текущий момент. Процессор EPYC 7H12 обладает 64 ядрами, как и другие старшие модели семейства EPYC Rome. Базовая частота новинки составляет 2,6 ГГц, а максимальная Turbo-частота достигает 3,3 ГГц. Для сравнения — возглавлявший до этого семейство Rome процессор EPYC 7742 обладает значительно более низкой базовой частотой в 2,25 ГГц, а вот в режиме Turbo может разгоняться чуть выше — до 3,4 ГГц. Средняя же рабочая частота новинки будет выше.

Источник изображения: AMD Базовая частота напрямую влияет на уровень TDP процессора. Поэтому показатель TDP EPYC 7H12 увеличился до 280 Вт, тогда как у EPYC 7742 он составлял 225 Вт. Из-за возросшего TDP новый процессор рекомендуется использовать в серверах с системами жидкостного охлаждения. Один из партнёров AMD, компания Atos, уже показала узел Bullsequana XH2000 с восемью процессорами EPYC 7H12 и полностью жидкостным охлаждением, высота которого составит лишь 1U. Кроме как частотами и уровнем TDP, процессоры EPYC 7H12 и EPYC 7742 ничем не отличаются друг от друга. Оба имеют 64 ядра Zen 2, 128 вычислительных потоков, 256 Мбайт кеш-памяти третьего уровня, 128 линий PCIe 4.0 и контроллер памяти с восемью каналами и поддержкой DDR4-3200.  Процессор EPYC 7H12 ориентирован на использование в составе высокопроизводительных вычислительных систем и центрах обработки данных. Согласно синтетическому тесту Linpack, новый процессор обеспечивает прирост производительности до 11 % по сравнению с EPYC 7742, который мы протестировали в августе. Цена новинки пока не названа. Не исключено, что она будет заметно выше, чем у 7742. Всё-таки, это особый сегмент рынка, где даже за незначительный прирост производительности готовы платить. Аналогичную политику проводит и Intel. В семействе Xeon на базе Broadwell были модели с индексом A, которые отличались чуть более высокими частотами. А летом Intel представила процессор Xeon Platinum 8284, который в сравнении с базовой моделью 8280 также имеет повышенную частоту и возросший в полтора раза ценник.

24.08.2019 [06:14], Андрей Галадей

IBM передала наработки по архитектуре Power сообществуКорпорация IBM сообщила, что переводит архитектуру набора команд (ISA) Power в разряд открытых решений. То есть, за неё не нужно будет платить, как это было в последние 6 лет. Отмечается, что с 2013 года действовал консорциум OpenPOWER, который лицензировал связанную с Power интеллектуальную собственность. Но теперь все наработки и патенты будут переданы сообществу безвозмездно. Сама же организация OpenPOWER Foundation будет переподчинена Linux Foundation, что позволит создать площадку для развития архитектуры без привязки к чипмейкеру или иной компании. Как отмечается, OpenPOWER Foundation включает в себя более 350 компаний, а сообществу передали свыше 3 млн строк кода системных прошивок, спецификаций и схем. Всё это позволит создавать Power-совместимые чипы всем желающим.

pixabay.com Помимо собственно процессоров, компания передала сообществу и смежные технологии для разработки расширений на основе интерфейсов OpenCAPI (Open Coherent Accelerator Processor Interface) и OMI (Open Memory Interface). Первая технология должна устранить «узкие места» во взаимодействии CPU, GPU, ASIC, а также других чипов и контроллеров. Вторая же должна ускорить оперативную память. Это позволит создавать на базе архитектуры Power специализированные чипы для искусственного интеллекта. Важно отметить, что процессоры Power позволяют создавать современные серверы и суперкомпьютеры. К примеру, суперкомпьютеры Summit и Sierra работают как раз на таких чипах. А это, на минуточку, первый и второй номера в мировом рейтинге таких систем. Напомним, на процессорах с архитектурой Power (хотя и специализированных) работали в том числе и консоли Sony PlayStation 3, Xbox 360, а также старые ПК и ноутбуки Apple.

27.07.2019 [15:15], Геннадий Детинич

Alibaba представила 16-ядерный RISC-V процессор XT 910 для «умной» периферии и edge-платформНа днях дочернее подразделение корпорации Alibaba Group компания Pingtouge Semiconductor на тематической конференции в Шанхае представила первый фирменный процессор для «умной» периферии. Китайская разработка XuanTie 910 оказалось уникальной по целому ряду причин, о которых мы поговорим ниже. Но прежде обозначим главное, на чём настаивают китайские источники. Процессор XuanTie 910 поможет китайским компаниям всех уровней сбросить зависимость от ядер ARM и других проприетарных разработок (читай ― сведут на нет опасность санкций со стороны США), поскольку ядра XuanTie 910 используют открытую архитектуру RISC-V с открытым набором команд.  Производительность моделей процессоров семейства XuanTie 910 может варьироваться в широких пределах. 64-бит ядра собираются в кластеры по четыре штуки. В процессоре может быть до четырёх таких кластеров, то есть в максимальной конфигурации XuanTie 910 имеет 16 ядер RISC-V. Больше вряд ли необходимо, но в случае надобности разработчики наверняка смогут увеличить число ядер в процессоре. Относительно небольшое число ядер в процессорах XuanTie 910 объясняется назначением платформы ― стать основой вещей с подключением к Интернету, ассистентов (умных колонок и прочего), самоуправляемых автомобилей, периферии с подключением к сетям 5G, платформ с элементами ИИ и тому подобных решений для перифейрийных (edge) вычислений и платформ. По словам разработчиков, XuanTie 910 сегодня является самым производительным решением на архитектуре RISC-V. Это решение на частоте 2,5 ГГц, изготовленное с использованием 12-нм техпроцесса, как заявлено, обеспечивает производительность на уровне 7,1 CoreMark/МГц, что на 40 % больше, чем для существующих сегодня конкурирующих процессоров на архитектуре RISC-V. Если точнее, то сравнение было с 64-бит ядром SiFive U74, которое достигает 5,1 CoreMark/МГц (на ядро). Оно тоже позиционируется как самое мощное решение RISC-V, способное исполнять полноценные ОС вроде Linux. Для сравнения — отечественный процессор Байкал-Т1, согласно нашим прошлогодним тестам, имеет производительность 5,4 CoreMark/МГц (на ядро).

onties.com Удивительным в этом сообщении наших коллег с EE Times представляется информация о 12-нм техпроцессе, который был задействован для производства XuanTie 910. Этот техпроцесс широко использует только компания GlobalFoundries. В этом случае Alibaba 100-процентно подставляется под санкции США, что нивелирует всякий смысл выбора открытой архитектуры. Впрочем, выводы делать рано, подождём подробности. Из других интересных особенностей ядер XuanTie 910 отметим 12-уровневый конвейер с внеочередным исполнением команд. За один цикл конвейер может исполнять сразу до 8 инструкций, причём и инструкции загрузки (load), и сохранения (store). Важно, что разработчики добавили в архитектуру RISC-V и процессор 50 новых расширенных инструкций для лучшей работы арифметических операций, доступа к памяти и поддержки многоядерности. Эти инструкции и ряд других решений китайцы сделают достоянием сообщества разработчиков с открытым кодом. Всё (или почти всё) будет выложено на GitHub, вероятно, в сентябре. Компании важно получить как можно более широкую поддержку со стороны независимых программистов, чему открытость RISC-V будет только способствовать. Примечательно, что новость о выходе XT 910 исчезла с сайта RISC-V Foundation через несколько часов после выхода.  Среди других заметных китайских участников RISC-V Foundation есть Huawei, MediaTek, Huami (партнёр Xiaomi), а также инвестгруппа Xiamen SIG. Сейчас Китай активно развивает импортозамещение. Согласно планам правительства, в 2020 году 40% спроса на полупроводниковую продукцию должны удовлетворить местные производители. В прошлом году, по данным TrendForce, лишь 15% пришлось на «домашние» процессоры.

16.04.2019 [17:05], Андрей Созинов

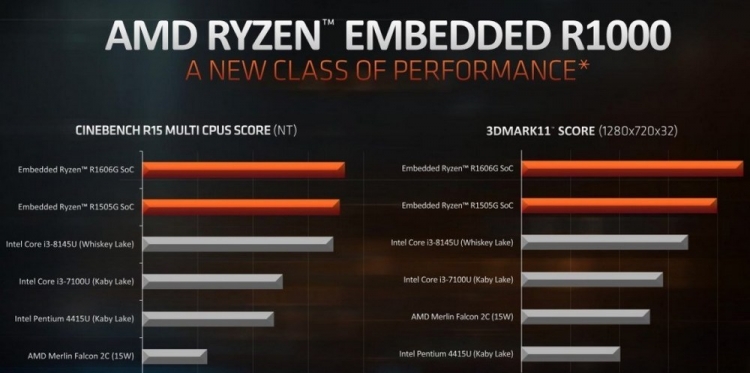

AMD Ryzen Embedded R1000: двухъядерные процессоры для встраиваемых системКомпания AMD расширила ассортимент своих продуктов для встраиваемых систем, представив новую серию процессоров Ryzen Embedded R1000. Новинки, по словам самой AMD, предлагают новый класс производительности в области встраиваемых систем, а также предлагают лучшее соотношение цены и производительности по сравнению с конкурентными решениями.

Источник изображений: AMD Всего было представлено два процессора: Ryzen Embedded R1606G и R1505G. Новинки весьма похожи друг на друга и отличаются между собой только тактовыми частотами ядер и встроенного GPU. Оба процессора располагают парой ядер Zen с поддержкой SMT, то есть работают на четыре потока. В качестве встроенного GPU в обеих новинках выступает Vega 3. В случае процессора Ryzen Embedded R1606G частоты ядер составляют 2,6/3,5 ГГц, а GPU — 1,2 ГГц. Младший Ryzen Embedded R1505G во всём медленнее на 200 МГц, то есть предлагает 2,4/3,3 и 1 ГГц соответственно. Объём кеша второго и третьего уровней составляет 1 и 4 Мбайт соответственно. Поддерживается оперативная память DDR4 с частотой до 2400 МГц. Также есть поддержка до двух 10-гигабитных портов Ethernet. Есть возможность подключения до трёх дисплеев. Максимальный поддерживаемый формат видео — 4K с частотой 60 FPS.  Производители систем на базе новинок AMD смогут самостоятельно настроить уровень TDP чипов в пределах от 12 до 25 Вт. Это, конечно же, будет несколько влиять на производительность, однако позволит использовать чипы как в более мощных компьютерах, так и в более экономичных, и даже безвентиляторных системах. По словам AMD, новинки могут найти применение в самых различных устройствах: от тонких клиентов до промышленных систем и игровых систем, вроде предстоящей Atari VCS. Также AMD отмечает высокую производительность своих новинок. В качестве примера приводятся результаты тестирования в Cinebench R15 и 3DMark11. Здесь оба процессора серии Ryzen Embedded R1000 смогли опередить чипы Intel Core i3-8145U поколения Whiskey Lake и Core i3-7100U поколения Kaby Lake.

02.04.2019 [20:00], Геннадий Детинич

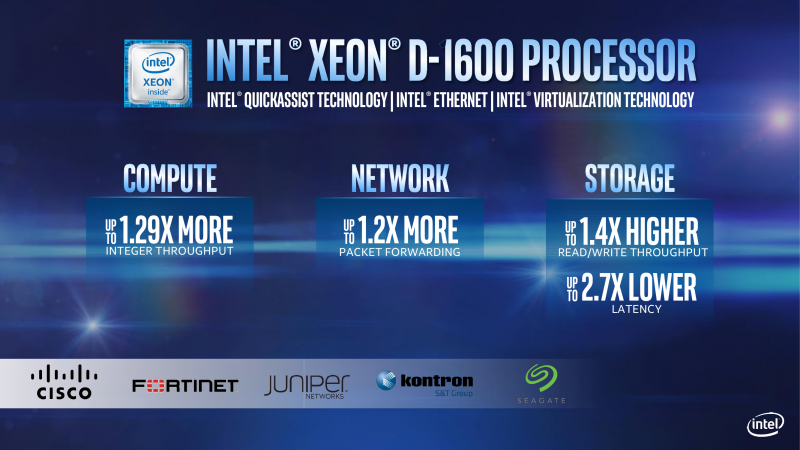

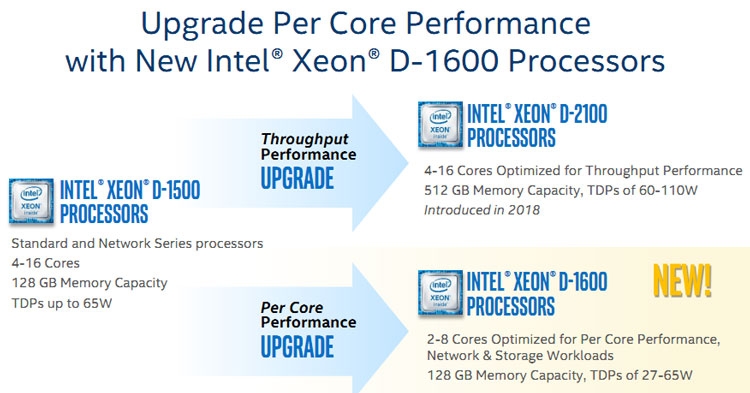

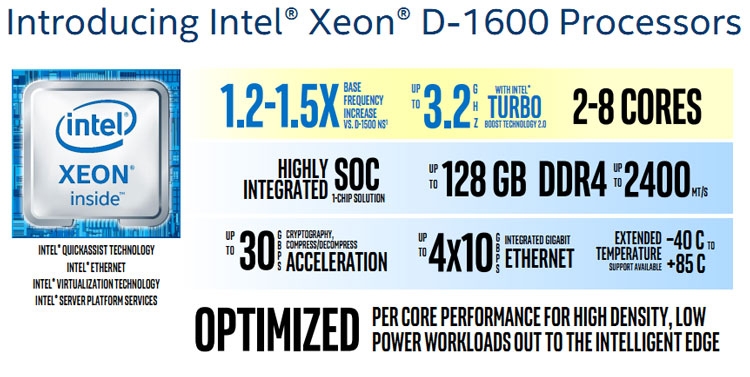

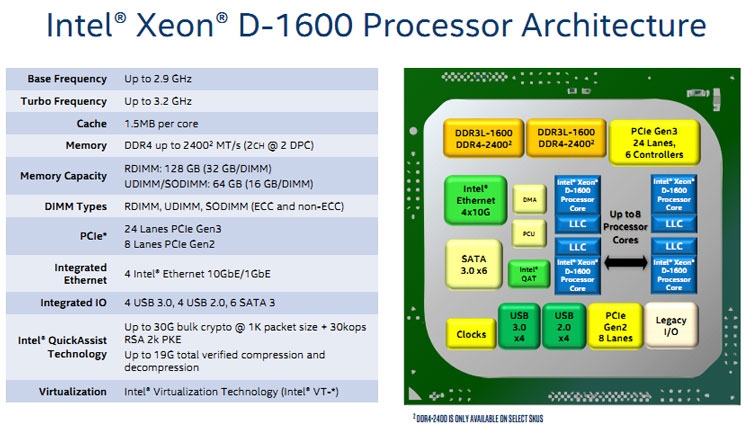

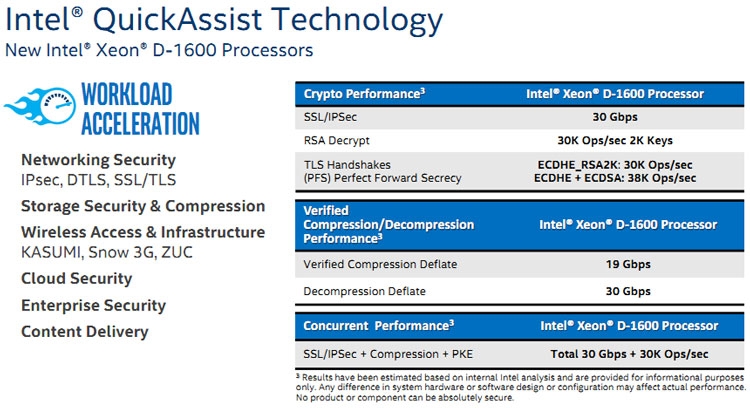

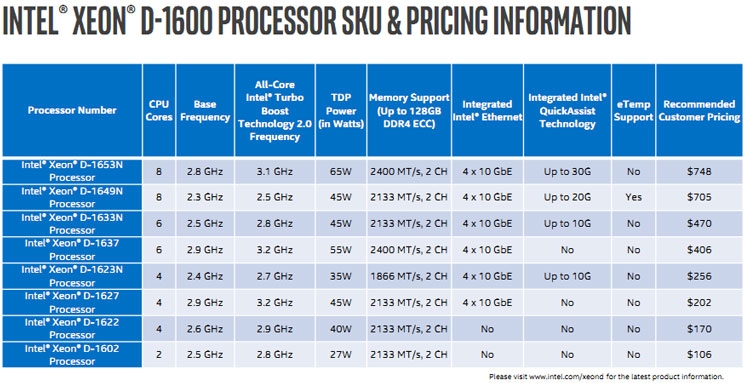

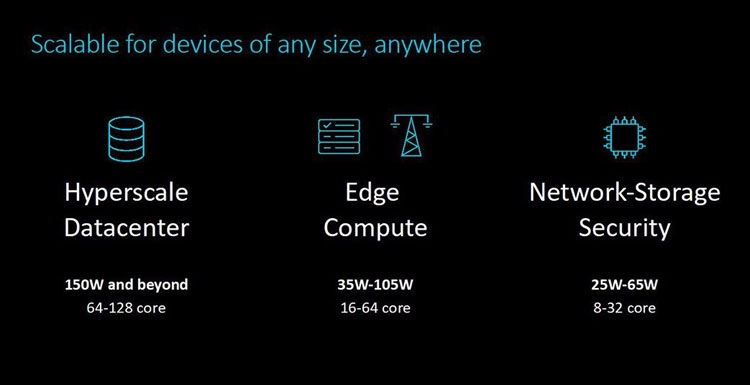

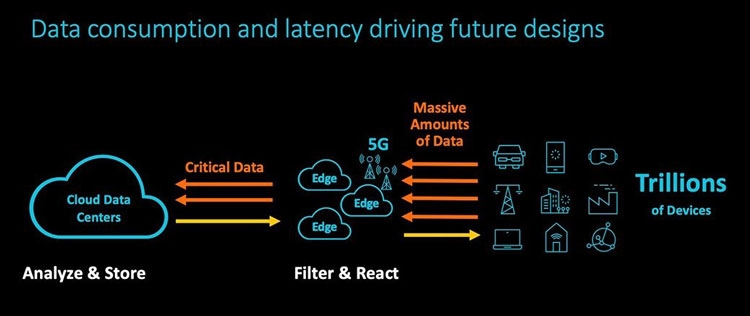

Intel представила процессоры Xeon D-1600: почта, телеграф, мостыВ 2015 году компания Intel представила процессоры Xeon семейства D. Первой появилась серия Xeon D-1500. Процессоры Xeon D получили архитектуру уровня Intel Core (Broadwell), став на ступеньку выше Xeon на архитектуре Atom. Целевое назначение Xeon D при этом не изменилось ― они всё так же были ориентированы на создание микросерверов, встраиваемых решений, систем для хранения данных малого и среднего уровней и сетевого оборудования. В 2018 году компания выпустила серию Xeon D-2100 на архитектуре Skylake. Тем самым в семейство Xeon D добавились решения повышенной производительности. Сегодня Intel представила третью серию Xeon D ― процессоры D-1600, которые возвращают нас к истокам семейства, главной целью которого был захват рынка производительной периферии с акцентом на плотность и сниженное потребление.  Процессоры Intel Xeon D-1600 получили меньшее число ядер, чем у их предшественников в лице Xeon D-1500. Диапазон числа физических ядер у моделей Xeon D-1600 сократился с 4–16 до 2–8. Максимальный тепловой пакет при этом остался тем же ― 65 Вт, тогда как минимальное значение TDP снизилось с 35 Вт до 27 Вт. Снижение числа ядер и сохранение максимального уровня TDP говорит о росте производительности в пересчёте на одно ядро. Во многом это достигается за счёт прироста как базовой частоты (в 1,2–1,5 раза), так и за счёт увеличения частоты при автоматическом разгоне до 3,2 ГГц, тогда как модели Xeon D-1500 в режиме турбо ограничивались частотой до 2,7 ГГц. Определённым образом Intel откатилась назад по шкале эволюции, понизив градус многоядерности в пользу наращивания однопоточной производительности. Собственно, этого требует позиционирование новой серии и активное развитие виртуализации сетевых функций (NFV). Для этого стала важнее скорость реакции сетевой платформы, что хорошо отрабатывается повышением тактовых частот.  Архитектурных изменений в моделях Xeon D-1600 не очень много, если они вообще есть (пока предполагаем, что архитектура осталась прежней ― Broadwell). Интегрированный контроллер памяти остался двухканальным с поддержкой модулей DDR4 с частотой до 2400 МГц суммарным объёмом до 128 Гбайт. Также поддерживается память DDR3L-1600. Уточним, процессоры Xeon D ― это однокристальная платформа, фактически SoC, что чрезвычайно удобно для тех областей, на которые нацелены эти решения. Встроенные в процессоры интерфейсы представлены 24 линиями PCIe 3.0, 8 линиями PCIe 2.0, 6 портами SATA 6 Гбит/с, 4 портами USB 3.0, 4 портами USB 2.0 и 4 портами Ethernet 10 Гбит/с. Кстати, об Ethernet. На кристалл Xeon D-1600 интегрирован контроллер Intel серии Ethernet 700. На это намекают не только четыре интерфейса Ethernet 10GbE, но также поддержка технологии Intel QuickAssist.  У старшей серии Xeon D-2100 модели Xeon D-1600 взяли то, чего не было у моделей Xeon D-1500 ― это поддержка технологии Intel QuickAssist (QAT). Технология QAT поддержана в моделях Xeon D-1600 с индексом «N». Наличие QAT означает, что процессор несёт встроенный аппаратный ускоритель для работы с криптографией, компрессией и обработки сетевого трафика. Поддерживается целый ряд популярных алгоритмов, что существенно разгружает вычислительные ядра и даёт ощутимый прирост производительности. Например, обработка трафика TLS/IPSec плюс компрессия происходит со скоростью 30 Гбит/с плюс 30 000 операций в секунду, как и расшифровка ключами RSA с такой же производительностью.  Поставки процессоров Xeon D-1600 компания Intel начнёт во втором квартале текущего года. Решения на основе новинок попадут на рынок к середине года или во второй его половине. По представлениям Intel, вычислительное и коммуникационное оборудование на базе Xeon D-1600 станет оптимальным выбором для развёртывания инфраструктуры для реализации и поддержки сотовой связи поколения 5G, а также для организации периферийных (пограничных) вычислений, когда обработка сырых данных (видео, сбор информации с датчиков, включая автомобильную электронику) происходит на месте и минимизирует пересылку в центры по обработке информации. Кроме того, они могут быть использованы в системах хранения данных.  Процессоры Intel Xeon D 1600 представлены в рамках большого обновления решений для ЦОД, которое включает «взрослые» Intel Xeon Cascade Lake AP и SP с поддержкой памяти Optane в формате DDR4-модулей и новых инструкций для ИИ, модульные FPGA Agilex и сетевые контроллеры 100GbE Intel Ethernet 800. Подробности по ссылкам ниже.

23.02.2019 [20:20], Геннадий Детинич

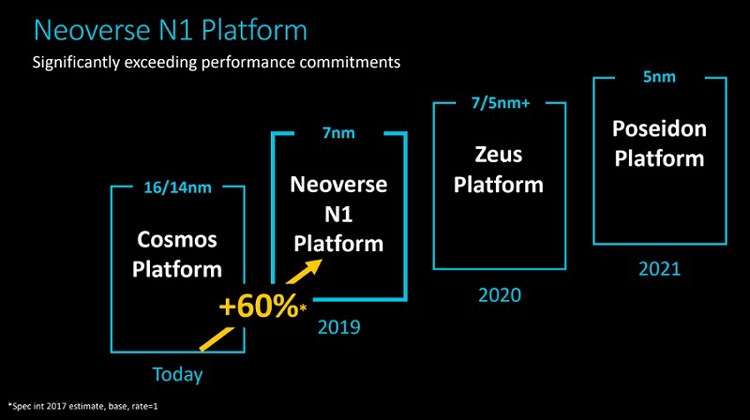

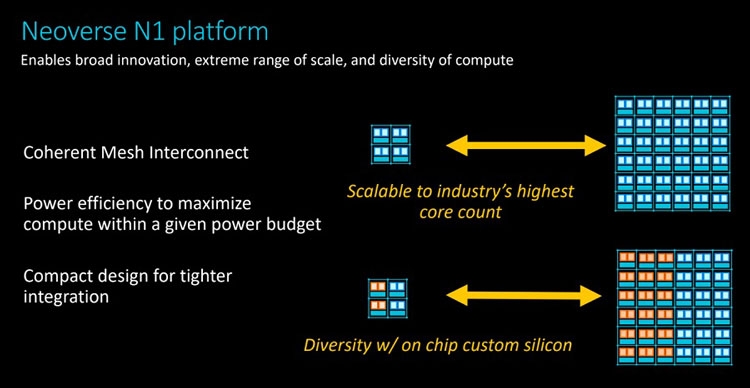

Анонс серверных платформ ARM Neoverse E1 и N1: шах и мат, IntelУж извините за столь кричащий заголовок, но ARM давно мечтает сказать нечто подобное в отношении серверных платформ Intel. Пока получается не очень. Как говорят в самой ARM, не вышло с первого раза, попробуем во второй. Не получится во второй раз, на третий точно всё будет как надо. А сейчас и повод-то отличный! Разработчики оригинальных ядер ARM из одноимённой компании ударили сразу с двух направлений: по масштабируемым сетевым платформам (Neoverse E1) и по масштабируемым серверным (Neoverse N1). Очевидно, что пока «мата» в этой партии явно не будет. Intel крепко держится за серверные платформы и одновременно тянет руки к периферийным как в виде распределённых вычислительных ресурсов в составе базовых станций, так и в виде обычных периферийных ЦОД. Тем не менее, шансы объявить Intel «шах» у ARM определённо есть.  Рассчитанную на несколько лет вперёд стратегию Neoverse компания ARM представила в середине октября прошлого года. Она предполагает три крупных этапа, в ходе которых будут выходить доступные для широкого лицензирования 64-битные ядра ARM Ares (7 нм), Zeus (7 и 5 нм) и Poseidon (5 нм). Планируется, что каждый год производительность решений будет возрастать на 30 %. Сама компания ARM, напомним, не выпускает процессоры и SoC, а лишь продаёт лицензии на ядра и архитектуру, которые клиенты компании обустраивают нужными им контроллерами и интерфейсами. У ARM настолько многочисленная армия клиентов, что она ожидает буквально цунами из сотен и тысяч миллиардов ядер в год уже в недалёком будущем. Когда-нибудь в этот водоворот ядер будут вовлечены и серверные платформы, а затем количество перейдёт в качество.  Разработка и анонс ядер Neoverse N1 ― это явление народу 7-нм ядер Ares. Процессоры могут нести от 4 до 128 ядер, объединённых согласованной ячеистой сетью. Платформа N1 может служить периферийным компьютером с 8-ядерным процессором с потреблением менее 20 Вт, а может стать сервером в ЦОД на 128-ядерных процессорах с потреблением до 200 Вт. Степень масштабируемости должна впечатлять. Кроме этого, как сообщают в ARM, производительность ядер N1 на облачных нагрузках в 2,5 раза выше, чем у 16-нм ядер предыдущего поколения Cosmos (Cortex-A72, A75 и A53). Кстати, прошлой осенью на платформе Cosmos компания Amazon представила фирменный процессор Graviton.  Производительность N1 при обработке целочисленных значений оказывается на 60 % больше, чем на ядрах Cortex-A72 Cosmos. При этом энергоэффективность ядер N1 также на 30 % выше, чем у ядер Cortex-A72. Как поясняют разработчики, платформа Neoverse N1 построена на «таких инфраструктурных расширениях, как виртуализация серверного класса, современная поддержка сервисов удалённого доступа, управление питанием и производительностью и профилями системного уровня».  Когерентная ячеистая сеть (Coherent Mesh Network, CMN), о которой выше уже говорилось, разработана с учётом высокого соответствия вычислительным возможностям ядер. По словам ARM, сеть обменивается с ядрами такой служебной информацией, которая позволяет устанавливать объём загрузки в память данных для упреждающей выборки, распределяет кеш между ядрами и определяет, как он может быть использован, а также делает много других вещей, которые способствуют оптимизации вычислений. Интересно отметить, что в составе процессоров на платформе Neoverse N1 может быть существенно больше 128 ядер, но с оптимальной работой возникнут проблемы. Точнее, вычислительная производительность упрётся в пропускную способность памяти. Так, ARM рекомендует для CPU с числом ядер от 64 до 96 использовать 8-канальный контроллер DDR4, а для 96–128 ядерных версий ― контроллер памяти DDR5. Платформа Neoverse E1 ― это решение для сетевых шлюзов, коммутаторов и сетевых узлов, которое, например, облегчит переход от сетей 4G к сетям 5G с их возросшей требовательностью к каналам передачи данных. Так, Neoverse E1 обещает рост пропускной способности в 2,7 раза, увеличение эффективности при передаче данных в 2,4 раза, а также более чем 2-кратный рост вычислительной мощности по сравнению с предыдущими платформами (ядрами). С масштабируемостью ядер E1 тоже всё в порядке, они позволят создать решение как для базовых станций начального уровня с потреблением менее 35 Вт, так и маршрутизатор с пропускной способностью в сотни гигабайт в секунду. Что же, ARM расставила на доске новые фигуры. Будет интересно узнать, кто же начнёт игру?

31.01.2019 [20:33], Сергей Карасёв

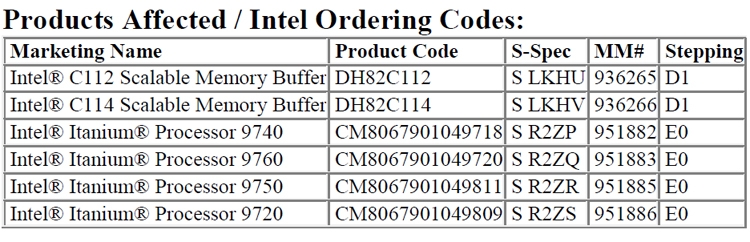

Intel ставит крест на процессорах ItaniumКорпорация Intel опубликовала документ, по сути, знаменующий закат эпохи процессоров Itanium, на которые некогда возлагались большие надежды.  В обнародованном уведомлении речь идёт о грядущем прекращении производства чипов Itanium 9700, известных под кодовым именем Kittson. Массовые поставки этих изделий были начаты в 2017 году. Семейство включает четыре модели — Itanium 9720, Itanium 9740, Itanium 9750 и Itanium 9760 с четырьмя и восемью вычислительными ядрами. В документе Intel говорится, что приём заказов на все перечисленные процессоры прекратится через год — 30 января 2020-го. Поставки будут полностью свёрнуты 29 июля 2021 года.  Таким образом, Intel ставит крест на решениях Itanium. Ещё в момент выхода Kittson говорилось, что эти изделия станут последними в семействе Itanium. Добавим, что впервые чипы Itanium дебютировали в мае 2001 года. Но продажи чипов оказались менее успешными, чем предполагалось. Основными причинами этому были проблемы с производительностью и малое количество оптимизированного программного обеспечения.

22.08.2018 [13:00], Геннадий Детинич

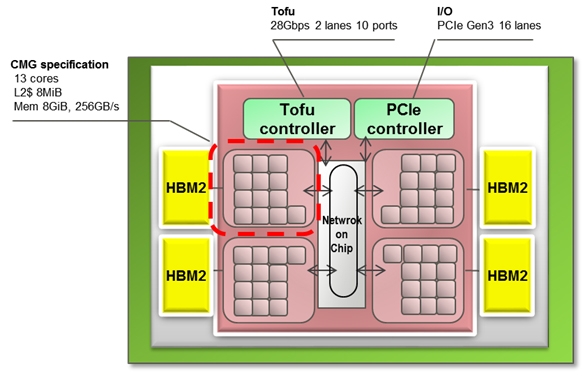

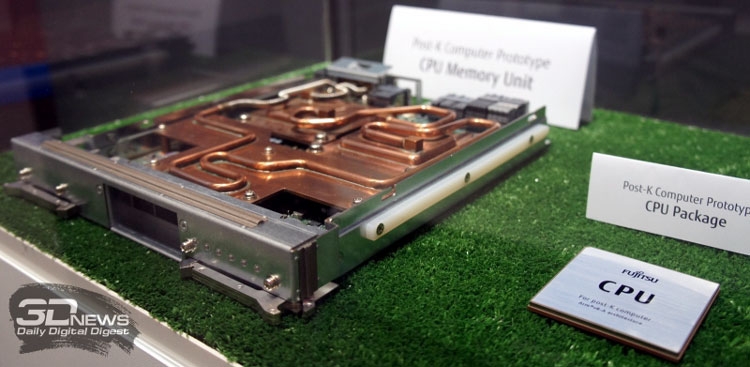

Раскрыты спецификации ARM-процессоров Fujitsu A64FX для суперкомпьютера Post-KПримерно через три года начнётся коммерческая эксплуатация суперкомпьютера Post-K, который компании Fujitsu и RIKEN разрабатывают на смену предыдущей совместной системы суперкомпьютера K (начал работать в 2011 году). Новая система Post-K обещает 100-кратно поднять производительность на уровне приложений. И сделано это будет благодаря переходу Fujitsu на ARM-совместимые ядра и новую архитектуру с масштабируемыми векторными инструкциями (Scalable Vector Extensions).  На прошедшей на днях конференции Hot Chips 30 (2018) компания Fujitsu впервые обнародовала спецификации новых процессоров, которые получили обозначение A64FX. Ни «A», ни «64», ни «FX» не имеют отношение к компании AMD, хотя в названии новых суперпроцессоров Fujitsu что-то немного согревает душу. Это процессоры с поддержкой 64-разрядных команд ARM и векторных инструкций длиной до 512 бит. Каждый процессор Fujitsu A64FX будет нести 48 вычислительных ядер и 4 вспомогательных ядра, разделённые на четыре блока, соединённых внутренней кольцевой шиной. Для связи с другими процессорами Fujitsu использует две линии внешнего интерфейса Tofu с пропускной способностью 28 Гбит/с. Строение процессора и внешний скоростной интерфейс обещают значительное наращивание параллелизма в вычислениях.

Fujitsu Каждый из 13-ядерных блоков поддержан кеш-памятью L2 объёмом 8 Мбайт. Кроме этого каждый из блоков напрямую обращается к модулю стековой памяти HBM2 объёмом 8 Гбайт. Суммарный объём памяти HBM2 у каждого процессора насчитывает 32 Гбайт, а общая скорость доступа достигает 1024 Гбайт/с. Поскольку память HBM2 можно рассматривать в качестве кеш-памяти третьего уровня, все или большинство операций выполняются в процессоре, что обещает отличный прирост производительности.  Процессор Fujitsu A64FX выпускается с использованием 7-нм техпроцесса, очевидно, что на линиях компании TSMC. Он насчитывает 8,7 млрд транзисторов. Пиковая производительность процессора для операций с двойной точностью достигает 2,7 терафлопс. Процессор без потерь на переход может вычислять операции с одинарной точностью и половинной, соответственно, в два и четыре раза быстрее. Также, за что надо благодарить тему машинного обучения, процессор A64FX оптимизирован для обработки 16- и 8-битных целочисленных значений.

07.07.2018 [13:35], Андрей Созинов

Китайский серверный процессор Hygon Dhyana построен на архитектуре AMD ZenКитайская компания Hygon начала производство x86-совместимых серверных процессоров Dhyana, построенных на микроархитектуре AMD Zen. Эти процессоры стали плодом совместной работы китайского производителя с компанией AMD, а именно лицензирования технологий последней, связанных с архитектурой x86. Компания AMD утверждает, что она не продаёт свои окончательные проекты чипов китайским партнёрам, а лишь позволяет создавать им свои собственные процессоры на основе её разработок, которые будут адаптированы именно к китайскому рынку. Но это лишь слова, и в реальности процессоры Hygon Dhyana настолько похожи на процессоры AMD EPYC, что разработчики Linux в обновление ядра для обеспечения их поддержки добавили лишь идентификаторы поставщика и номера семейств. А коды поддержки для новых китайских процессоров были полностью заимствованы у EPYC. То есть между процессорами практически нет разницы.

Источник изображений: AMD Новые китайские серверные процессоры появились как раз во время обостряющейся торговой войны между Китаем и США, так что собственное производство процессоров является стратегически важным для КНР. Также начать производство собственных процессоров Китай подстегнуло то, что в 2015 году администрация Обамы запретила Intel продавать Поднебесной процессоры Xeon из-за того, что они помогают в развитии её ядерной программы.  То, что AMD смогла создать франшизу, которая позволяет китайским производителям процессоров создавать и продавать x86-совместимые процессоры, на этом фоне выглядит ещё более удивительно. Как это удалось американской компании? Если вкратце, то AMD создала в Китае совместное предприятие с местными частными и государственными компаниями. В итоге получилось достаточно сложная структура, но она позволяет лицензировать AMD технологии, связанные с архитектурой x86, не нарушая какие-либо законы или соглашения, с той же Intel.

09.11.2017 [13:07], Сергей Карасёв

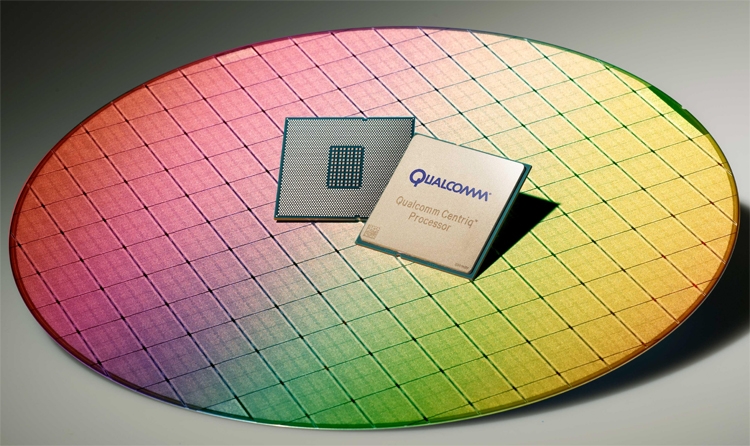

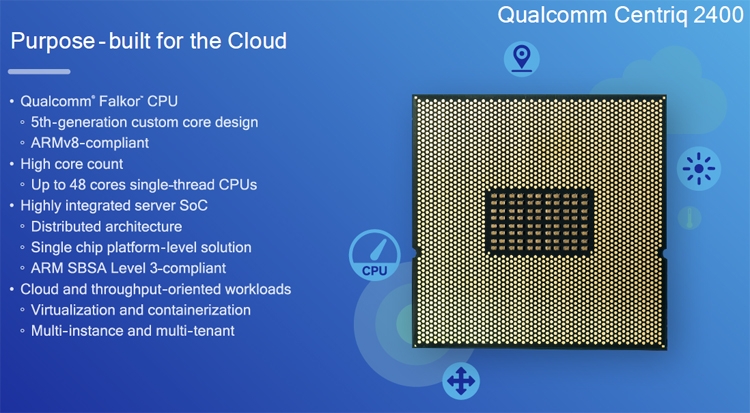

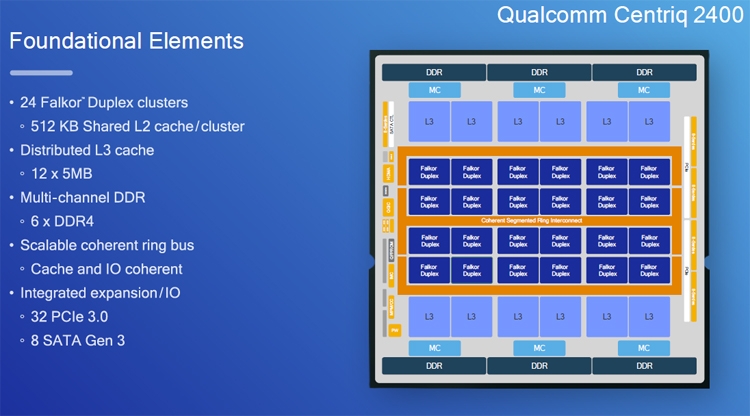

Начались коммерческие поставки 10-нм серверных чипов Qualcomm Centriq 2400Компания Qualcomm Datacenter Technologies, подразделение Qualcomm Incorporated, объявила о старте коммерческих поставок первых в мире 10-нанометровых серверных процессоров — решений семейства Centriq 2400. О разработке чипов Centriq 2400 стало известно ещё в декабре прошлого года. Позднее Qualcomm раскрыла детали об этих изделиях. И вот теперь настало время массовых поставок процессоров.

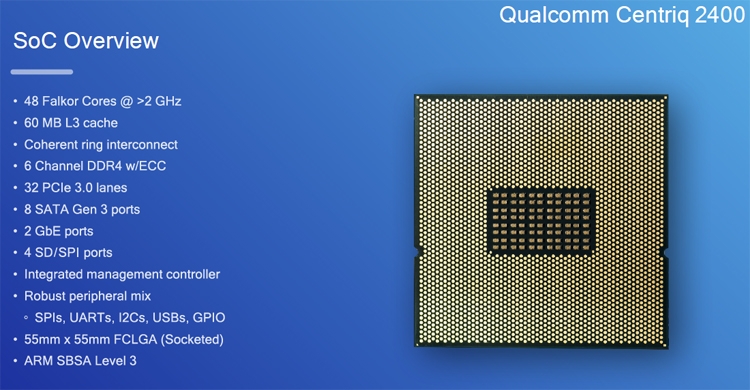

Источник изображений: Qualcomm В основу Centriq 2400 положены 64-битные вычислительные ядра с кодовым именем Falkor, обладающие поддержкой команд ARMv8. Количество таких ядер в составе чипов может достигать 48. Максимальная тактовая частота — 2,6 ГГц.  При изготовлении изделий применяется 10-нанометровая технология Samsung FinFET. Процессоры насчитывают до 18 млрд транзисторов. Каждая пара ядер снабжена 512 Кбайт общей кеш-памяти L2, а объём кеша L3 у чипов достигает 60 Мбайт.  В состав Centriq 2400 вошли 6-канальный контроллер памяти с поддержкой DDR4-2667 МГц ECC (до двух модулей на канал), 32 линии PCI Express 3.0, интерфейсы SATA, USB и пр.  Процессоры ориентированы на современные облачные платформы и центры обработки данных. Более подробную информацию о технических характеристиках можно найти здесь. Что касается стоимости, то изделие Qualcomm Centriq 2460, насчитывающее 48 вычислительных ядер, обойдётся заказчикам в 1995 долларов США. |

|