Материалы по тегу: cpu

|

16.05.2024 [01:05], Игорь Осколков

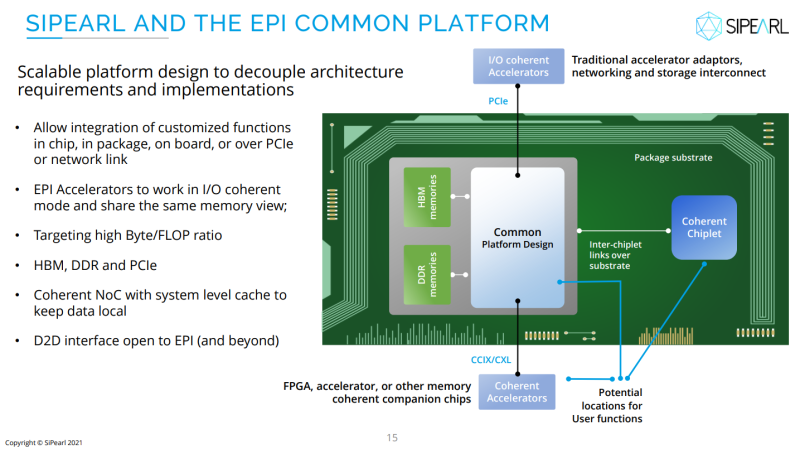

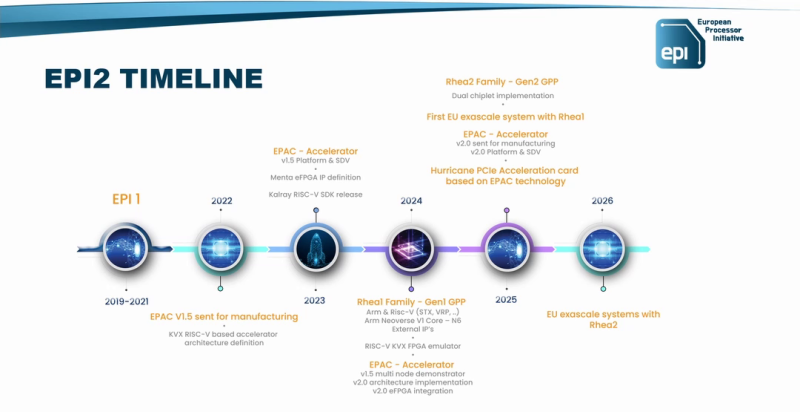

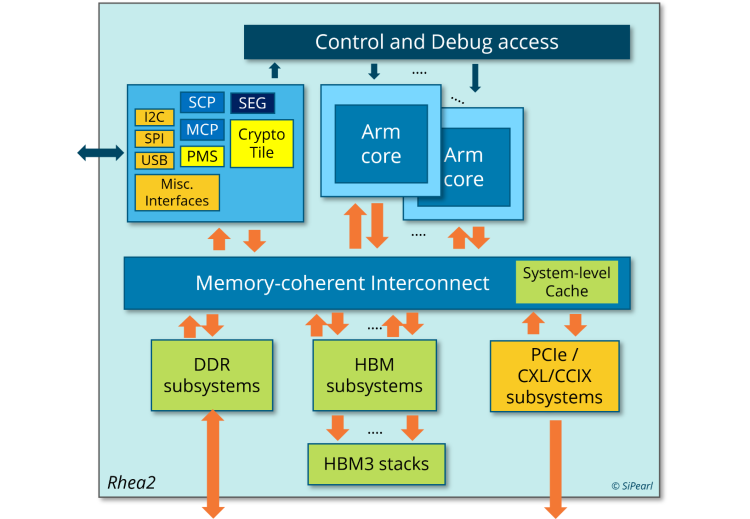

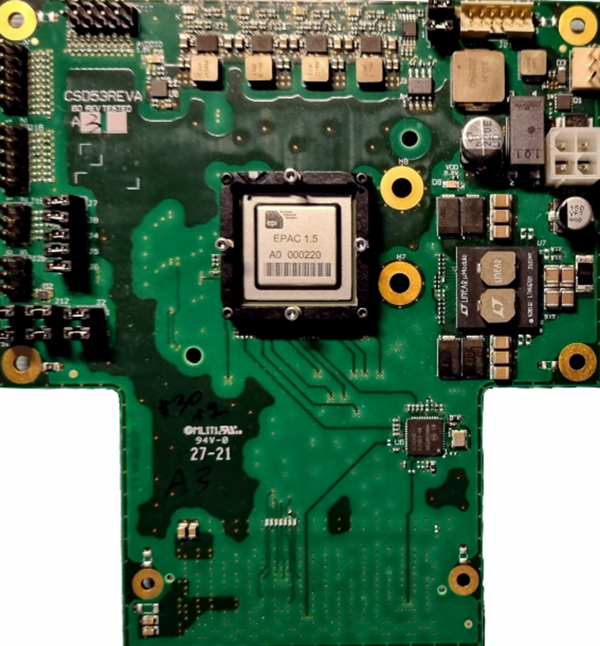

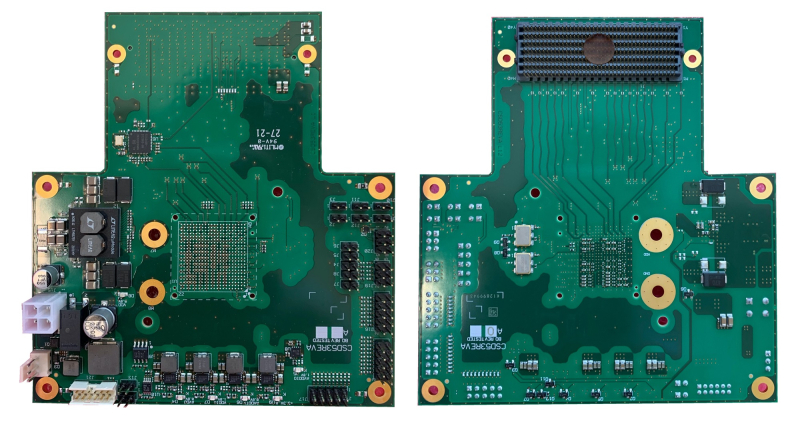

И для ИИ, и для HPC: первые европейские серверные Arm-процессоры SiPearl Rhea1 получат HBM-памятьКомпания SiPearl уточнила спецификации разрабатываемых ею серверных Arm-процессоров Rhea1, которые будут использоваться, в частности, в составе первого европейского экзафлопсного суперкомпьютера JUPITER, хотя основными чипами в этой системе будут всё же гибридные ускорители NVIDIA GH200. Заодно SiPearl снова сдвинула сроки выхода Rhea1 — изначально первые образцы планировалось представить ещё в 2022 году, а теперь компания говорит уже о 2025-м. При этом существенно дизайн процессоров не поменялся. Они получат 80 ядер Arm Neoverse V1 (Zeus), представленных ещё весной 2020 года. Каждому ядру полагается два SIMD-блока SVE-256, которые поддерживают, в частности, работу с BF16. Объём LLC составляет 160 Мбайт. В качестве внутренней шины используется Neoverse CMN-700. Для связи с внешним миром имеются 104 линии PCIe 5.0: шесть x16 + две x4. О поддержке многочиповых конфигураций прямо ничего не говорится. Очень похоже на то, что SiPearl от референсов Arm особо и не отдалялась, поскольку Rhea1 хоть и получит четыре стека памяти HBM, но это будет HBM2e от Samsung. При этом для DDR5 отведено всего четыре канала с поддержкой 2DPC, а сам процессор ожидаемо может быть поделён на четыре NUMA-домена. И в такой конфигурации к общей эффективности работы с памятью могут быть вопросы. Именно наличие HBM позволяет говорить SiPearl о возможности обслуживать и HPC-, и ИИ-нагрузки (инференс). На примере Intel Xeon Max (Sapphire Rapids c 64 Гбайт HBM2e) видно, что наличие сверхбыстрой памяти на борту даёт прирост производительности в означенных задачах, хотя и не всегда. Однако это другая архитектура, другой набор инструкций (AMX), другая же подсистема памяти и вообще пока что единичный случай. С Fujitsu A64FX сравнения тоже не выйдет — это кастомный, дорогой и сложный процессор, который, впрочем, доказал эффективность и в HPC-, и даже в ИИ-нагрузках (с оговорками). В MONAKA, следующем поколении процессоров, Fujitsu вернётся к более традиционному дизайну. Пожалуй, единственный похожий на Rhea1 чип — это индийский 5-нм C-DAC AUM, который тоже базируется на Neoverse V1, но предлагает уже 96 ядер (48+48, два чиплета), восемь каналов DDR5 и до 96 Гбайт HBM3 в четырёх стеках, а также поддержку двухсокетных конфигураций. AWS Graviton3E, который тоже ориентирован на HPC/ИИ-нагрузки, вообще обходится 64 ядрами Zeus и восемью каналами DDR5. Наконец, NVIDIA Grace и Grace Hopper в процессорной части тоже как-то обходятся интегрированной LPDRR5x, да и ядра у них уже Neoverse V2 (Demeter), и своя шина для масштабирования имеется. В любом случае в 2025 году Rhea1 будет выглядеть несколько устаревшим чипом. Но в этом же году SiPearl собирается представить более современные чипы Rhea2 и обещает, что их разработка будет не столь долгой как Rhea1. Компанию им должны составить европейские ускорители EPAC, тоже подзадержавшиеся. А пока Европа будет обходиться преимущественно американскими HPC-технологиями, от которых стремится рано или поздно избавиться.

12.05.2024 [21:43], Владимир Мироненко

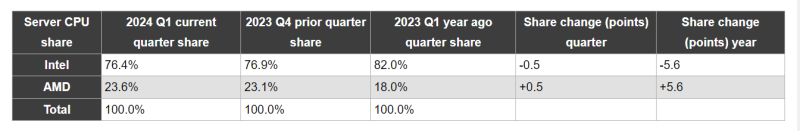

Доля AMD на рынке серверных процессоров выросла в I квартале 2024 года до 23,6 %Согласно данным компании Mercury Research, которая отслеживает рынки полупроводников и компонентов для ПК, Intel продолжает доминировать на рынке чипов для ПК, но AMD завоёвывает позиции на рынках чипов для серверов, десктопов и мобильных устройств, пишет AnandTech. В I квартале 2024 года AMD достигла рекордно высокой доли на рынках процессоров с архитектурой x86 для десктопов и серверных процессоров x86 благодаря успеху продуктов серии Ryzen 8000 и процессоров EPYC Genoa. Хотя доля AMD на рынке настольных компьютеров и ноутбуков в последние годы колебалась, компания неуклонно расширяет присутствие на рынке серверов как по объёмам поставок, так и по росту доходов. В I квартале 2024 года доля AMD на рынке процессоров для серверов увеличилась до 23,6 %, что означает прирост на 0,5 % последовательно и на 5 % год к году, обусловленный ростом числа платформ на базе процессоров AMD EPYC Genoa. Intel продолжает доминировать на рынке серверов с долей 76,4 %, но прогресс AMD вполне очевиден. Доля выручки AMD на рынке серверов на платформе x86 достигла 33 %, что на 5,2 % больше год к году и на 1,2 % больше, чем в предыдущем квартале. Это означает, что компания набирает обороты в производстве hi-end устройств с современными процессорами. Учитывая, что на данный момент у Intel нет прямых конкурентов 96-ядерным и 128-ядерным (Bergamo) процессорам AMD, неудивительно, что AMD удалось добиться увеличения доли на рынке чипов для серверов. «Как мы отметили во время нашего финансового отчёта за I квартал, продажи серверных процессоров выросли по сравнению с прошлым годом благодаря росту внедрения на предприятиях и расширению облачных развертываний», — указала AMD в своём заявлении.

06.05.2024 [20:05], Сергей Карасёв

AMD начала поставки образцов процессоров EPYC TurinКомпания AMD, по сообщению ресурса AnandTech, обнародовала свежую информацию о планах по выпуску серверных процессов EPYC Turin (7005) на архитектуре Zen 5. Говорится, что образцы этих чипов уже поставляются клиентам, тогда как их официальный выход на рынок состоится во II половине текущего года. По имеющейся информации, изделия EPYC Turin будут использовать существующий сокет SP5 (LGA 6096). Готовятся обычные (Zen 5) и «облачные» (Zen 5c) варианты. В первом случае будут задействованы 16 вычислительных чиплетов CCD (до восьми ядер в каждом), что в сумме даст до 128 ядер. Для «облачных» версий предусмотрено наличие 12 чиплетов CCD (до 16 ядер в каждом), а суммарное количество ядер Zen 5с составит до 192 (384 потока). Как отметила глава AMD Лиза Су (Lisa Su), по сравнению с процессорами предыдущего поколения EPYC Turin обеспечат значительное увеличение производительности и энергоэффективности, что позволит компании укрепить позиции на серверном рынке. По её словам, для новой платформы партнёры AMD проектируют примерно на 30 % больше систем, нежели для EPYC Genoa. Вместе с тем, подчеркивает Су, изделия этих двух поколений какое-то время будут сосуществовать, что поможет клиентам выработать оптимальную стратегию обновления инфраструктуры. По мнению руководителя AMD, переход с Genoa на Turin займёт меньше времени, чем это было в случае Milan и Genoa. В корпоративном секторе, по словам госпожи Су, AMD тесно сотрудничает с Dell, HPE, Lenovo, Supermicro и другими разработчиками серверов. В текущем квартале начнётся массовое производство ряда ИИ-платформ на базе ускорителей Instinct MI300X. AMD прогнозирует, что выручка от поставок GPU-решений для дата-центров в 2024 году превысит $4 млрд. Еще в январе компания называла цифру в $3,5 млрд. Таким образом, AMD рассчитывает на существенное увеличение продаж продуктов для ЦОД.

30.04.2024 [13:02], Сергей Карасёв

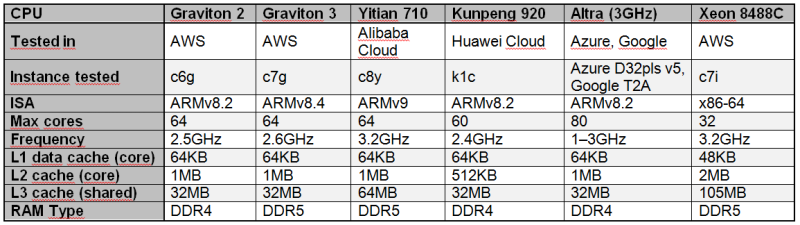

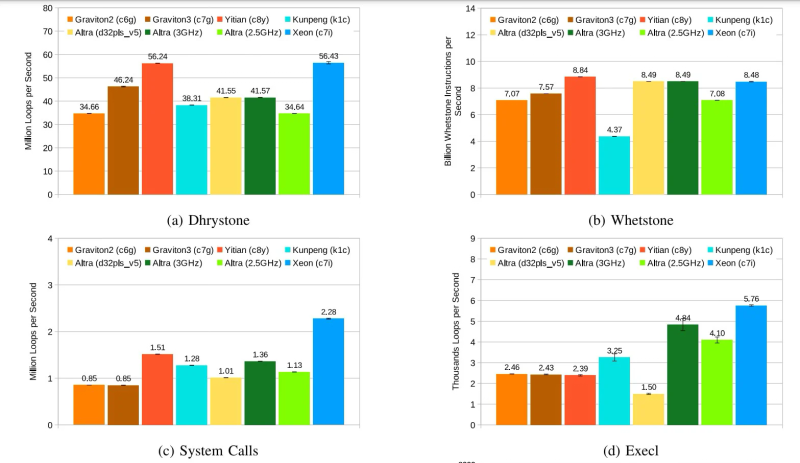

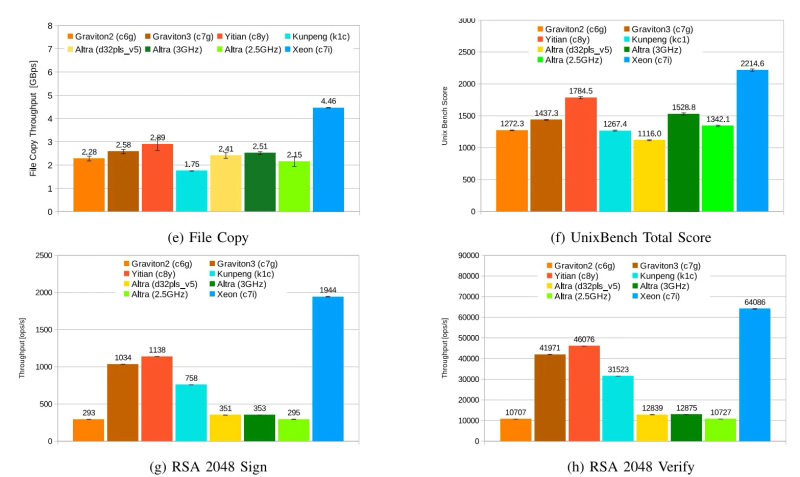

Alibaba Yitian 710 признан самым быстрым облачным Arm-процессором в ряде бенчмарковСогласно результатам исследования, обнародованным Институтом инженеров электротехники и электроники (IEEE) в журнале Transactions on Cloud Computing, процессор Alibaba Yitian 710 на сегодняшний день является самым производительным серверным чипом с архитектурой Arm из тех, которые доступны в составе различных облачных платформ, передаёт The Register. Изделие Yitian 710 было создано подразделением T-Head специально для нужд Alibaba Cloud и дебютировало в 2021 году. Этот 5-нм процессор на базе Armv9 насчитывает до 128 ядер с частотой до 3,2 ГГц. Обеспечивается поддержка восьми каналов памяти DDR5 и 96 линий PCIe 5.0. При этом чипы отличаются высокой энергетической эффективностью. Alibaba Cloud рассчитывала перенести пятую часть своих мощностей на собственные Arm-чипы к 2025 году. В ходе исследования чип Yitian 710 в конфигурации с 64 ядрами сравнивался с Arm-процессорами Amazon Graviton 2/3 (64 ядра), Huawei Kunpeng 920 (60 ядер) и Ampere Altra (80 ядер), а также с х86-чипом Intel Xeon Platinum 8488C поколения Sapphire Rapids. Тестирование проводилось в различных облачных средах, включая Amazon Web Services (AWS), Alibaba Cloud, Huawei Cloud, Microsoft Azure, Google Cloud Platform. Оценивалось быстродействие при выполнении различных задач: классические бенчмарки Dhrystone и Whetstone, ряд системных вызовов ядра и вызовов execl, скорость копирования файлов, показатель UnixBench, подписи и аутентификация с использованием криптографического алгоритма RSA 2048, а также работа с СУБД. Как отмечается, практически во всех перечисленных тестах процессор Alibaba опережал конкурирующие чипы с архитектурой Arm. В задачах Whetstone изделие Yitian 710 также превзошло процессор Xeon Platinum и чип Altra. Вместе с тем Graviton 3 показал превосходство в тесте Redis. Тем не менее, Yitian 710 сохранил своё преимущество в двух из трёх задач RocksDB. В плане эффективности чипам Arm требуется больше системных вызовов, чем их конкурентам Intel. Но в некоторых сценариях использования решения Arm всё равно оказываются более предпочтительными.

09.04.2024 [23:45], Сергей Карасёв

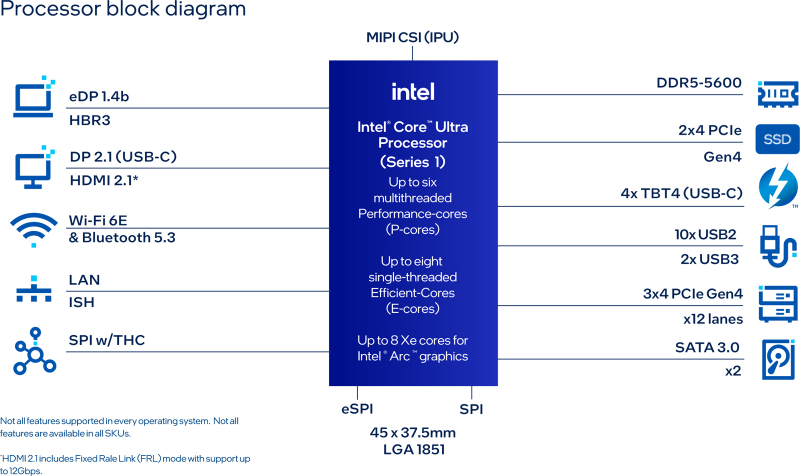

Intel представила чипы Meteor Lake PS, Raptor Lake PS и Atom x7000RE для edge-устройствКорпорация Intel анонсировала сразу три семейства процессоров для встраиваемых устройств и edge-оборудования: это чипы Core Ultra Meteor Lake PS, Core Raptor Lake PS и Atom x7000RE. Изделия серии Core Ultra PS (Meteor Lake) изготавливаются по технологии Intel 4. Они рассчитаны на установку в разъём нового поколения LGA 1851. Конструкция включает ядра P-cores и E-cores, графический блок Intel Arc GPU, а также нейропроцессорный движок (NPU), предназначенный для ускорения ИИ-операций.

Источник изображения: Intel Семейство Core Ultra PS представлено моделями HL со стандартным значением TDP в 45 Вт и UL с базовым TDP в 15 Вт. Реализована поддержка оперативной памяти DDR5-5600 и до 20 линий PCIe 4.0. В общей сложности в серию Core Ultra PS вошли девять моделей. Количество ядер достигает 16, число одновременно обрабатываемых потоков инструкций — 22. Объём кеша L3 составляет до 24 Мбайт, тактовая частота — до 5,0 ГГц. В свою очередь, процессоры семейства Core PS (Raptor Lake) используют сокет LGA 1700. Эти чипы также подразделяются на подсерии HL и UL с базовым TDP соответственно 45 и 15 Вт. Они содержат до 14 ядер с поддержкой до 20 потоков инструкций. Поддерживается работа с оперативной памятью DDR5–5200 и DDR4-3200. Возможно использование 8 линий PCIe 4.0 в дополнение к 12 линиям PCIe 3.0 в составе интегрированного PCH. Используется графика Intel Graphics. Объём кеша L3 достигает 24 Мбайт, тактовая частота — до 5,2 ГГц. В семейство Core PS на сегодняшний день входят 14 моделей.

Наконец, изделия Atom x7000RE (Amston Lake) выполнены по технологии Intel 7. Они насчитывают до восьми ядер E-cores, а показатель TDP варьируется от 6 до 12 Вт. Поддерживаются память LPDDR5-4800, DDR5-4800 и DDR4-3200, до девяти линий PCIe 3.0, графика Intel UHD Graphics. Максимальная тактовая частота — 3,6 ГГц.

02.04.2024 [21:13], Алексей Степин

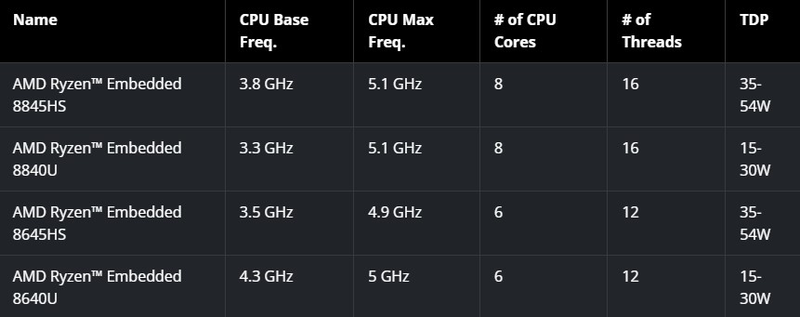

Три в одном: AMD представила процессоры Ryzen Embedded 8000 с интегрированными NPU и GPUКомпания AMD продолжает активно развивать направление процессоров для встраиваемых систем: если в начале года она представила гибридную платформу Embedded+, сочетающую в себе архитектуру Zen и ПЛИС Versal, то сегодня анонсировала процессоры Ryzen Embedded 8000 с интегрированным ИИ-сопроцессором. Это первое решение AMD для промышленного применения, сочетающее в себе целых три архитектуры: классическую процессорную Zen 4, графическую RDNA 3 и предназначенную для ИИ-вычислений XDNA. Новые процессоры должны найти применение в системах машинного зрения, робототехнике, промышленной автоматике и многих других сценариях.

Источник: AMD AMD говорит о производительности в ИИ-сценариях, достигающей 39 Топс, что в рамках теплопакета, не превышающего у старшей модели 54 Вт, выглядит неплохо. Но в данном случае речь идёт о совокупной производительности всех архитектур, на долю же NPU приходится только 16 Топс. В качестве памяти используется двухканальная DDR5-5600 с поддержкой ECC. Благодаря графическому ядру RDNA 3 новые Ryzen Embedded 8000 смогут выводить информацию на четыре экрана с разрешением 4K, а также обеспечивать кодирование и декодирование всех популярных видеоформатов, включая H.264, H.265 и AV1. Для связи со специфическими ускорителями или контроллерами оборудования чипы получили 20 линий PCI Express 4.0.  На момент анонса в серию Ryzen Embedded 8000 вошли четыре процессора — два шестиядерных (8645HS и 8640U) и два восьмиядерных (8845HS и 8840U), оба варианта поддерживают SMT и имеют тактовые частоты в диапазоне от 3,3 до 5,1 ГГц. Теплопакет у новинок конфигурируемый, в зависимости от условий охлаждения он может варьироваться либо в пределах 15–30 Вт или 35–54 Вт, что позволит обойтись пассивным теплоотводом там, где это необходимо. Новые решения AMD будут сопровождаться средствами SDK, поддерживающими Windows, а также популярные ИИ-фреймворки PyTorch и TensorFlow. В том числе анонсированы уже обученные модели, которые доступны на HuggingFace. В деле построения экосистемы для Ryzen Embedded 8000 компания тесно сотрудничает с известными производителями оборудования, в том числе с Advantech, ASRock и iBASE. Также для новых процессоров заявлен удлинённый жизненный цикл.

04.03.2024 [17:00], Руслан Авдеев

Евросоюз намерен добиться полупроводникового суверенитета, используя архитектуру RISC-VВ Евросоюзе активно инвестируют в инициативы, призванные обеспечить полупроводниковый суверенитет благодаря использованию открытой архитектуры RISC-V. EE Times сообщает, что инициативу курирует Барселонский суперкомпьютерный центр (Barcelona Supercomputing Center или BSC) — пионер в разработке европейских решений RISC-V. Страны ЕС беспокоит полупроводниковая зависимость от иностранных компаний, и это беспокойство усугубляется относительно недавним дефицитом чипов в мире. В то же время за использование в своих решениях архитектуры RISC-V никому не надо платить и ни у кого не нужно получать разрешений на её применение, поэтому технология так привлекательна для разработчиков. BSC представляет собой один из ведущих исследовательских центров Европы. Он играет ключевую роль в разработке чипов на архитектуре RISC-V и возглавляет несколько проектов, связанных с этой технологией, в частности, European Processor Initiative (EPI). В рамках инициативы EPI стоимостью €70 млн разрабатывается новое поколение высокопроизводительных процессоров. Связанная с BSC компания OpenChip должна найти коммерческое применение разработанным технологиям. BSC начал создавать собственные чипы семейства Lagarto довольно давно — первые 65-нм варианты представили ещё в мае 2019 года. Сегодня речь идёт уже о четвёртом поколении, которое будет выпускаться в соответствии с 7-нм техпроцессом. Центр работает и с другими европейскими компаниями и исследовательскими организациями над созданием комплексной экосистемы RISC-V, включающей ПО, ОС и компиляторы. Подобные инициативы должны снизить зависимость Евросоюза от американских и азиатских производителей — отсутствие в ЕС зрелой индустрии высокопроизводительных чипов расценивается как значимая уязвимость. Европа считает, что RISC-V — идеальная платформа для достижения суверенитета, при этом бесплатная. Впрочем, эксперты признают, что о полной независимости не может быть речи из-за сложности экосистемы полупроводниковой индустрии. Но у Европы есть большая база знаний и потенциал разработки новых решений, предпринимаются и шаги к организации производства. В BSC уже экспериментировали с Arm-процессорами, но после Brexit и приобретения компании Arm группой Softbank, выяснилось, что собственной региональной технологии у ЕС нет, тогда и обратили внимание на общедоступную RISC-V. В 2019 году Еврокомиссию убедили в необходимости начать выпуск чипов на этой архитектуре для суперкомпьютеров. В числе других европейских компаний, предлагающих RISC-V продукты, есть Gaiser, Esperanto Technologies, Semidynamics и Codasip, но они уделяют больше внимания процессорам и ускорителям, а не конечным готовые решения. По оценкам экспертов, в Евросоюзе компаний, работающих с RISC-V, пока недостаточно. Тем не менее, организаторы новых инициатив предостерегают от нереалистичных ожиданий и призывают к стратегическому сотрудничеству — для производства требуются не только разработки, но и сырьё, высокоточное оборудование, и др. Европа может рассчитывать на выпуск решений в пределах 7-нм, более современные техпроцессы пока слишком дороги. Впрочем, ЕС уже добился значительного прогресса в достижении полупроводникового суверенитета с помощью RISC-V.

23.02.2024 [01:27], Алексей Степин

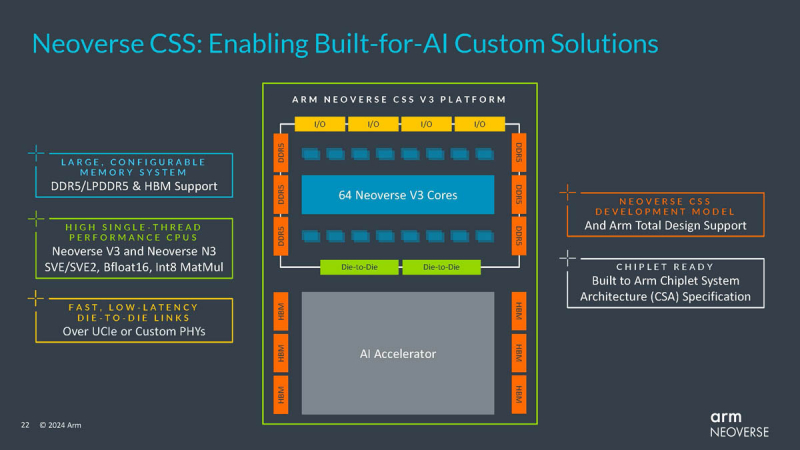

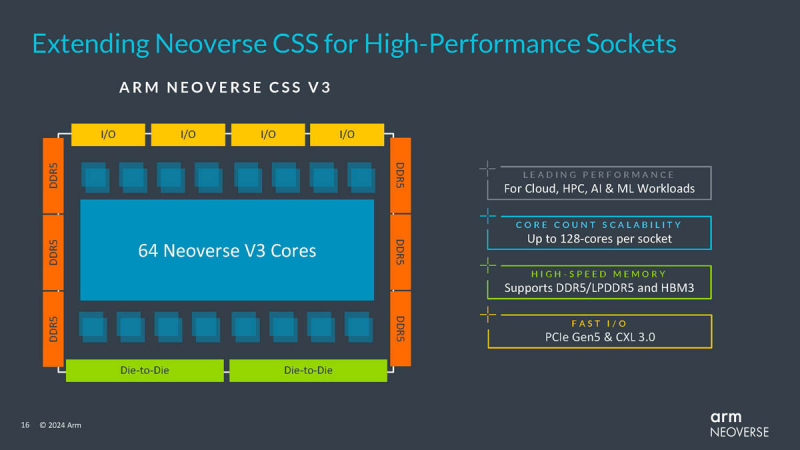

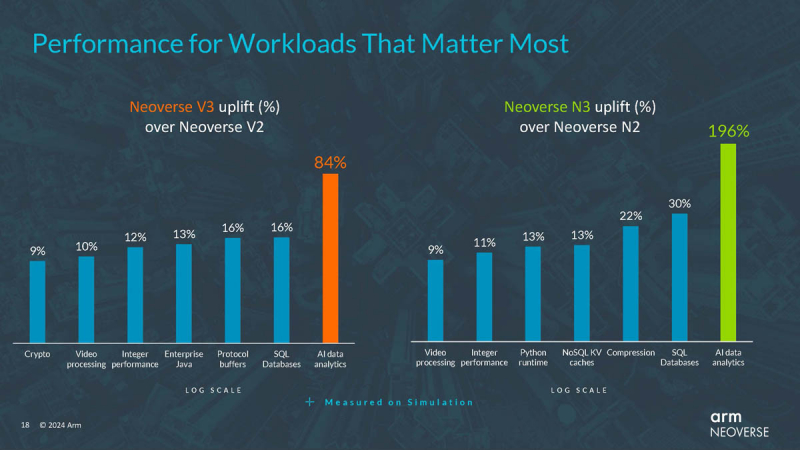

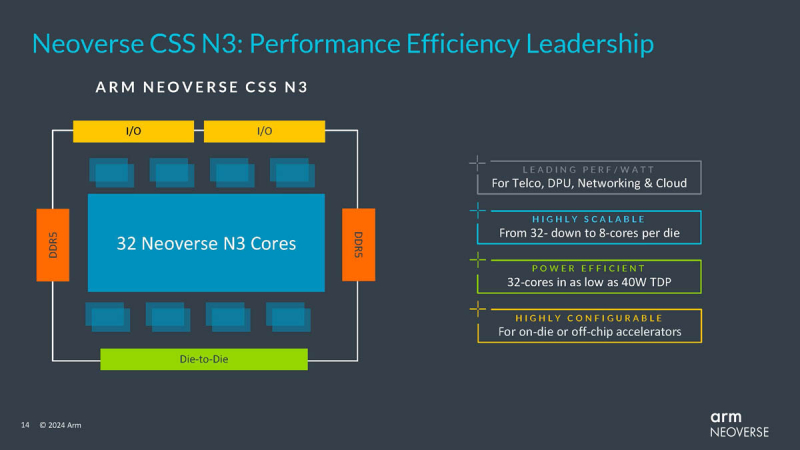

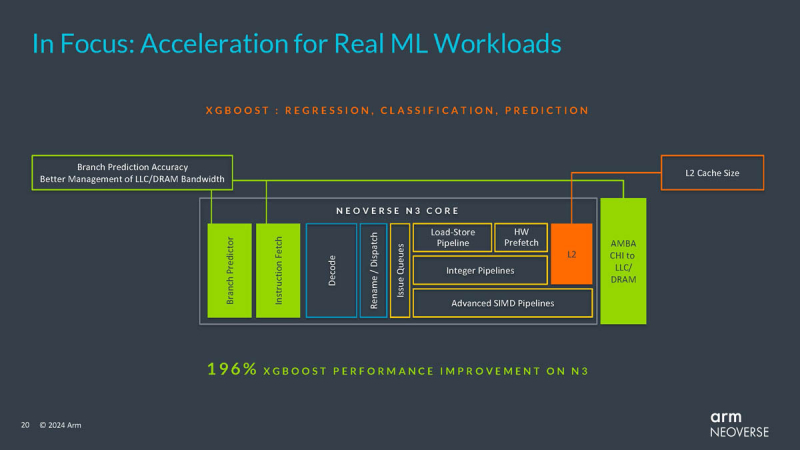

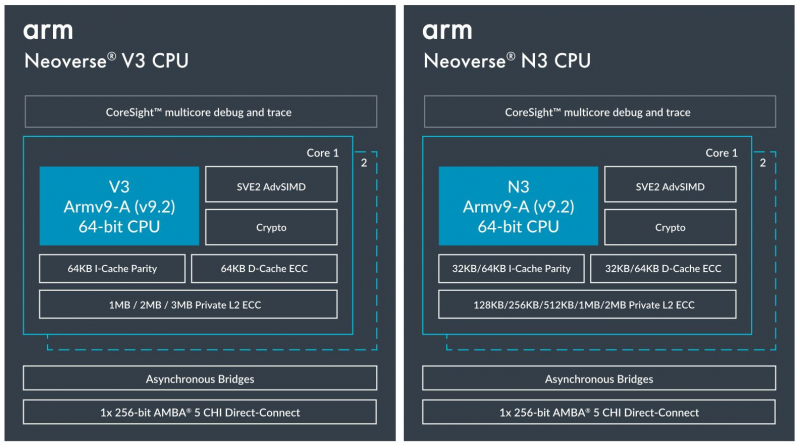

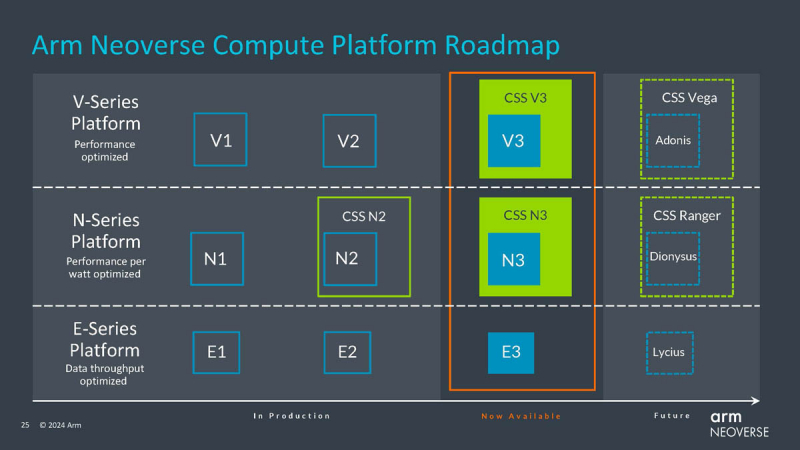

Arm представила процессорные ядра Neoverse N2 и V3: упор на ИИКомпания Arm продолжает развивать инициативу Neoverse Compute Subsystem (CSS), анонсировав два новых ядра, Neoverse N3 (Hermes) и V3 (Poseidon), рассчитанных на техпроцессы 2–5 нм. Они являются преемниками N2 (Perseus) и V2 (Demeter), а упор в их архитектуре сделан главным образом на повышении производительности в задачах ИИ. Платформа CSS представляет собой комплект IP-блоков Arm, включающий в себя помимо собственно процессорных ядер подсистемы интерконнекта, контроллеры памяти, блоки ввода-вывода и управления питанием и тому подобную «обвязку», облегчающую создание и вывод на рынок новых SoC. Будущие процессоры на базе Neoverse V3 получат до 64 ядер Armv9-A (v9.2) на кристалл и до 128 на сокет — в виде сборки из двух 64-ядерных кристаллов. Каждый из таких кристаллов получит шесть каналов (LP)DDR5, но также заявлена поддержка HBM3. Поддерживаются двухсокетные конфигурации. Более того, у V3 есть два блока для объедениия с чиплетами, а основным интерфейсом является UCIe 1.1, причём Arm прямо говорит о возможности подключения ИИ-ускорителя, как это сделано в NVIDIA Grace Hopper. Помимо интерконнекта для чиплетных сборок V3 будет располагать собственными контроллерами I/O с поддержкой PCIe 5.0 и CXL 3.0 — до 64 линий. В подавляющем большинстве сценариев прирост относительно V2, обещанный Arm, не слишком велик и составляет от 9 % до 16 %, но вот производительность в ИИ-задачах подтянута аж на 84 %, что однозначно указывает на позиционирование новых ядер — это, в первую очередь, рынок гиперскейлеров, которые сегодня почти поголовно заинтересованы в применении ИИ-технологий. Сами ядра имеют по 64 Кбайт L1-кеша для инструкций и данных и до 3 Мбайт L2-кеша. Интереснее всего поддержка SVE2, но ширину и количество этих SIMD-блоков компания не раскрывает. В N3 ядер меньше, от 8 до 32, а главным улучшением снова стала повышение энергоэффективности. Относительно N2 процессор N3 будет на 20 % быстрее в пересчёте на Вт. Максимальный теплопакет для 32-ядерного варианта составит всего 40 Вт. Этот дизайн должен найти своё применение в DPU и телекоммуникационных решениях. Сами ядра здесь точно такие же, что в V3, но L1-кеши можно урезать до 32 Кбайт, а L2-кеш не может быть больше 2 Мбайт. N3 также поддерживает объединение двух блоков ядер в одном чипе, двухсокетные конфигурации и UCIe-подключение стороннего чиплета, но для этого тут есть только один блок. Количество линий PCIe 5.0/CXL 3.0 вдвое меньше, до 32 шт. Каналов памяти (LP)DDR5 всего четыре. Прирост по сценариям применения относительно N2 здесь выглядит иначе: серьёзное внимание уделено задачам сжатия и декомпрессии данных и работе с СУБД. Однако упор на ИИ-нагрузки тут даже более серьёзный, нежели у старшего собрата — прирост производительности может достигать 196 % относительно N2. Правда, в случае и N3, и V3 речь идёт о вполне конкретной библиотеке XGBoost. В арсенале Arm также есть ядро E3, о котором, впрочем, компания пока ничего не рассказала. Упомянуто лишь, что эта платформа ориентирована на сценарии с «прокачкой» больших объёмов данных. Заодно компания поделилась именами будущих решений четвёртого поколения. Платформа V-серии получит имя Vega с процессорными ядрами Adonis, N-серия станет называться Ranger с ядрами Dionysus, а E-серия пока никак не названа, но для ядер выбрано имя Lycius. Arm не без оснований считает новые платформы и ядра лучшим поколением Neoverse на данный момент. Компания уверена в том, что за её экосистема станет основой вычислительных решений нового поколения, в том числе для ИИ. Конкурировать новым решениям предстоит, в том числе, с лучшими процессорами Intel и AMD. Сама Intel собирается поддерживать разработку технологий на базе Arm, предоставляя как интеллектуальную собственность, так и производственные мощности. Последние два года стали для Arm весьма успешным в деле освоения рынка ЦОД. NVIDIA представила Grace и Grace Hopper, AWS создала уже четвёртое поколение собственных процессоров Graviton, Microsoft показала свой первый CPU Cobalt 100, да и Google трудится над процессорами Maple и Cypress. А основатель Oracle, которая активно перебирается на чипы Ampere, и вовсе считает, что архитектура Intel x86 теряет актуальность для серверов. Про доминирование Arm в сегменте DPU и говорить нечего.

20.12.2023 [16:13], Сергей Карасёв

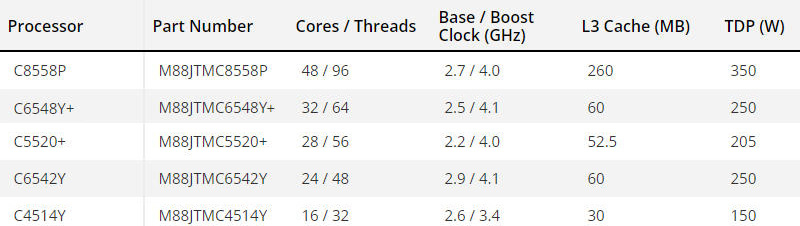

Intel Xeon Emerald Rapids на китайский лад: представлены чипы Jintide 5-го поколения с 48 ядрамиКитайская компания Montage Technology, по сообщению ресурса Tom's Hardware, анонсировала процессоры Jintide 5-го поколения для местного рынка. По сути, это новейшие серверные чипы Intel Xeon Emerald Rapids с незначительно изменённой маркировкой и модифицированным набором поддерживаемых технологий. В 2016 году Intel организовала партнёрский проект с китайским университетом Цинхуа и Montage Technology Global Holdings, Ltd. для создания продуктов, ориентированных на рынок серверов и ЦОД в КНР. В рамках сотрудничества поставляются чипы Jintide на базе Xeon разных семейств. В начале 2023 года компании представили серию процессоров Jintide на базе Sapphire Rapids. В серию Jintide 5-го поколения на момент анонса вошли пять моделей: C8558P, C6548Y+, C5520+, C6542Y и C4514Y. Фактически это китайские варианты процессоров Xeon Platinum 8558P, Xeon Gold 6548Y+, Xeon Gold 5520+, Xeon Gold 6542Y и Xeon Silver 4514Y. Число вычислительных ядер составляет от 16 до 48; во всех случаях поддерживается технология многопоточности. Показатель TDP варьируется от 150 до 350 Вт (см. характеристики ниже).

Источник изображения: Montage Technology Чипы Jintide получили дополнительные средства мониторинга и аппаратного шифрования: это технологии PrC (Pre-check) и DSC (Dynamic Security Check). От оригинальных Xeon Emerald Rapids унаследованы такие возможности, как поддержка восьми каналов памяти DDR5-5600 суммарным объёмом до 4 Тбайт и 80 линий PCIe 5.0. Изделия Jintide могут применяться в двухпроцессорных серверах.

Источник изображения: Tom's Hardware На данный момент семейство Jintide 5-го поколения ограничено перечисленными моделями, и не до конца ясно, собирается ли Montage Technology выпускать другие версии. Напомним, в серии Xeon Emerald Rapids доступны процессоры с количеством ядер до 64.

15.12.2023 [00:30], Алексей Степин

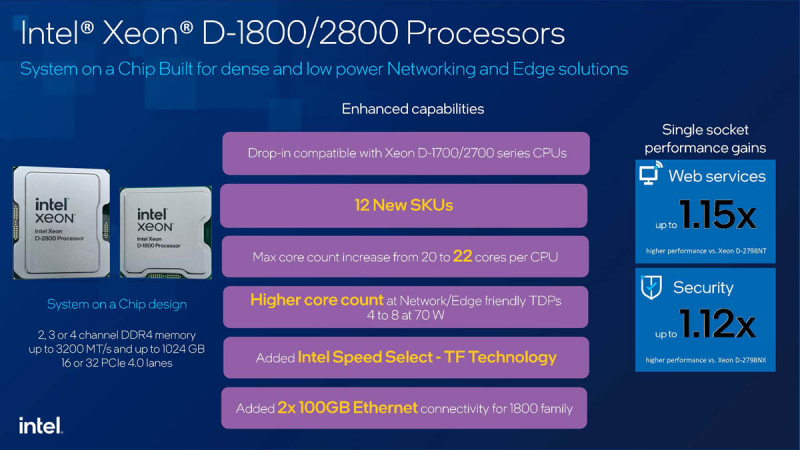

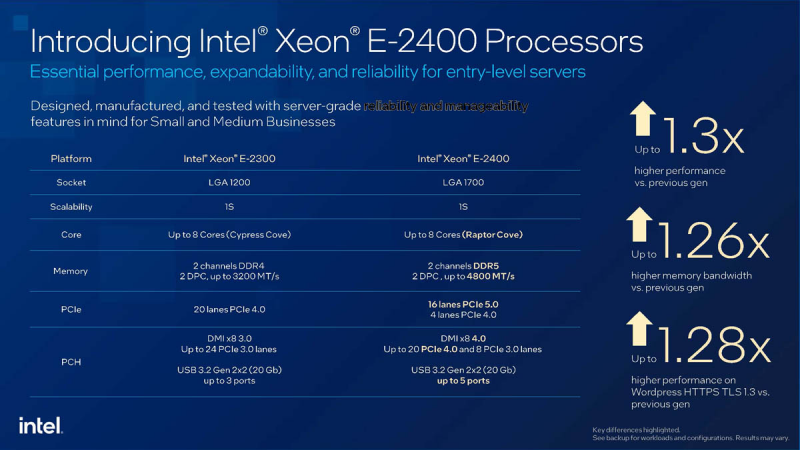

Intel представила процессоры Xeon D-1800/2800 и E-2400 для edge-систем и серверов начального уровняНаряду с анонсом процессоров Xeon Scalable пятого поколения компания Intel обновила и модельные ряды Xeon D и Xeon E. Изменений и нововведений в представленных чипах достаточно много. Так, модельный ряд Xeon D по традиции поделён на две ветви: Xeon D-1800 и Xeon D-2800. Уже сериии Xeon D-1700 и D-2700 были адаптированы для работы в серверах периферийных вычислений и в составе сетевого оборудования. Напомним ключевые моменты:

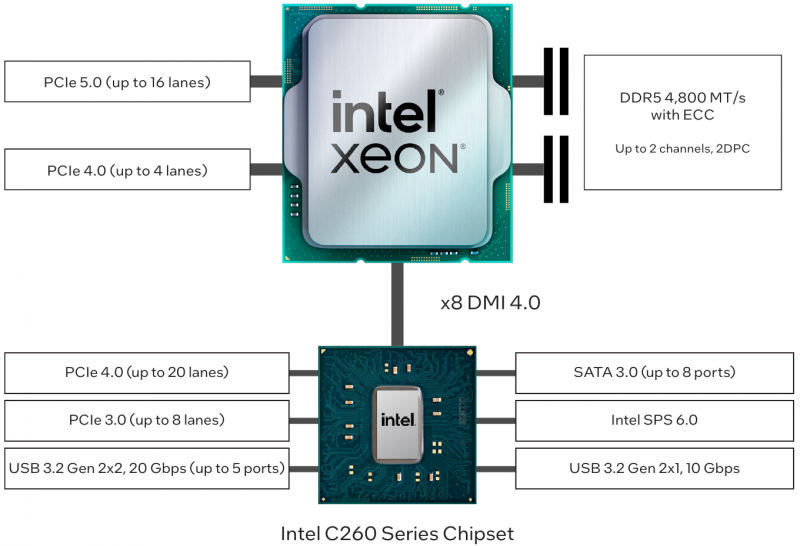

Всё это характерно и для новых Xeon D-1800 и D-2800, ведь в их основе лежит прежняя архитектура Ice Lake-D. Речь всё ещё идёт о сочетании DDR4 и PCI Express 4.0, однако улучшения всё же есть: оптимизация техпроцесса позволила довести максимальное количество ядер до 22 против 20 у предыдущих моделей при неизменном теплопакете. Небольшой прирост производительности тоже есть — примерно 1,12-1,15х у старшей модели Xeon D-2800. Кроме того, процессоры Xeon D-1800, наконец, получили поддержку двух 100GbE-портов. Одновременно с анонсом новых Xeon D состоялся анонс серии Xeon E-2400, которая заменит Xeon E-2300. Изменений здесь существенно больше. Во-первых, платформа перебралась с LGA 1200 на LGA 1700, а на смену ядрам Cypress Cove пришли Raptor Cove. И хотя E-ядер в составе CPU нет, Intel почему-то решила не активировать поддержку AVX-512. Во-вторых, существенный апгрейд претерпела подсистема памяти: вместо двух каналов DDR4-3200 теперь доступна пара каналов DDR5-4800. Наконец, Xeon E-2400 получили поддержку PCI Express 5.0 — из 20 имеющихся процессорных линий 16 теперь способны работать именно в этом режиме. Подросла версия DMI с 3.0 до 4.0, а PCH новой платформы теперь предоставляет 20 линий PCIe 4.0 и 8 линий PCIe 3.0. Заодно с трёх до пяти выросло количество портов USB 3.2 Gen 2x2 (20 Гбит/с). Максимальное число ядер в новой серии Xeon E осталось прежним — их всё ещё восемь, но благодаря существенно более быстрой памяти и использованию техпроцесса Intel 7 Ultra производительность новинок в среднем в 1,3 раза выше, чем у предшественников. Базовая частота подросла до 3,5 ГГц, в турборежим частота доходит до 5,6 ГГц, но при этом теплопакет не выходит за рамки 95 Вт. Нацелены Intel Xeon E-2400 на рынок серверов и облачных систем начального уровня. |

|