Материалы по тегу: arm

|

18.10.2019 [20:36], Алексей Степин

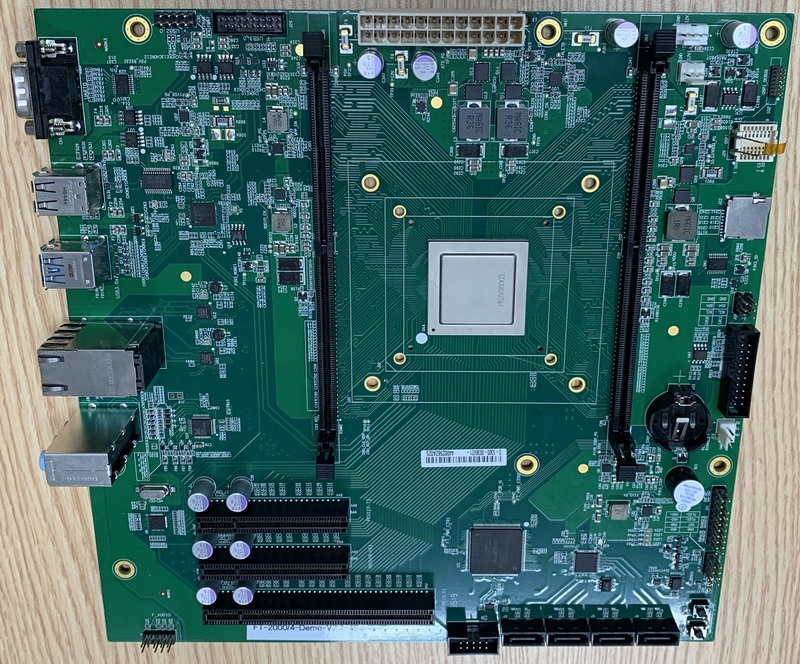

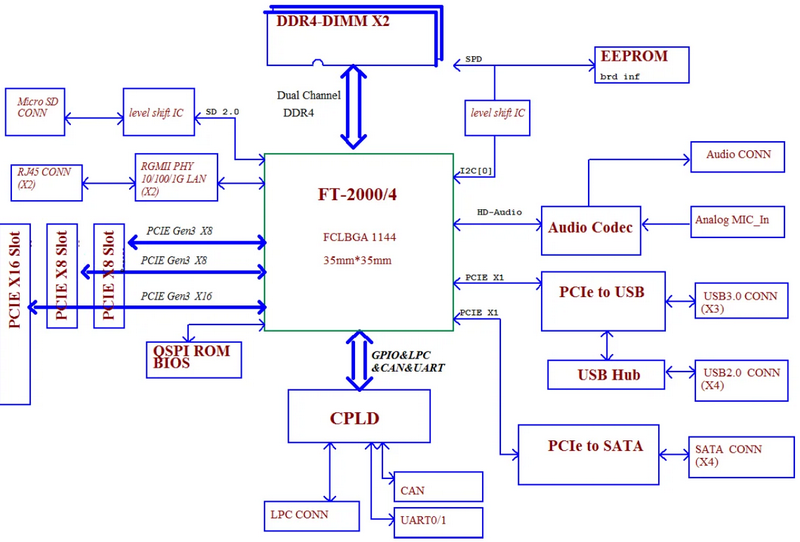

ARMv8 на китайский лад — представлена Micro-ATX плата с 3-ГГц Phytium FT2000/4Китайская компания-разработчик Phytium, известная созданием CPU для суперкомпьютеров Tiahne-1A и Tiahne-2, занимавших первую строку в рейтинге TOP500, уже несколько лет работает над новым поколением 64-ядерных ARMv8-процессоров FeiTeng FT-2000 для будущего Tiahne-3. В сентябре компания анонсировала упрощённый вариант CPU всего с четырьмя ядрами — Phytium FT2000/4. А на днях в сети была замечена первая системная плата формата Micro-ATX на базе этой SoC.

Так выглядит системная плата на базе данного ЦП Phytium FT2000/4 производится с использованием 16-нм техпроцесса TSMC, диапазон его тактовых частот лежит в пределах 2,6-3,0 ГГц. Имеется 4 Мбайт кеша L2 (по 2 Мбайт на пару ядер) и 4 Мбайт общего кеша L3. Теплопакет невелик и не превышает 10 Вт. Процессор размером 35 × 35 мм имеет упаковку FCBGA 1144.

Возможности процессора FT2000/4 SoC предлагает 34 линии PCI-Express 3.0: две x1 и две x16, которые можно разделить, получив четыре x8. Линни x1 отведены под контроллеры USB 3.0 (3 скоростных порта и 4 версии 2.0) и Serial ATA (4 порта). Также есть встроенные интерфейсы HD Audio и 1GbE. Кроме того, имеется отдельный блок аппаратного ускорения шифрования, поддерживающий китайские стандарты SM2/SM3/SM4. Память работает в двухканальном режиме, но слотов DDR4 DIMM всего два, что может ограничить её объём. Встроенного графического адаптера нет, однако есть поддержка некоторых чипов AMD Radeon и GPU китайского производителя Jingjia. На уровне ПО заявлена совместимость с Linux-дистрибутивом Kylin OS. Phytium позиционирует FT2000/4 как основу для создания промышленных компьютеров, встраиваемых решений, тонких клиентов и терминалов (в том числе ноутбуков и моноблоков). А новая материнская плата пригодится для разработчиков. Как упомянутых выше решений, так и приложений для будущего суперкомпьютера.

30.09.2019 [11:00], Андрей Созинов

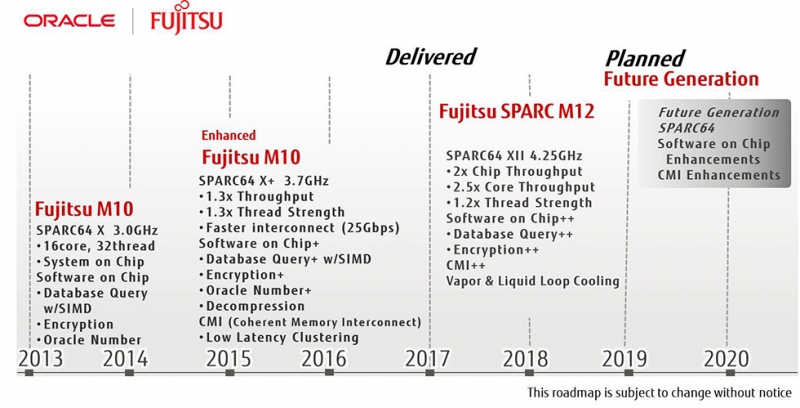

Конец эпохи? Oracle сворачивает SPARC-бизнес и инвестирует в ARMКомпания Oracle объявила, что инвестировала $40 млн в компанию Ampere Computing, которая занимается разработкой 64-разрядных ARM-процессоров серверного класса. Похоже, компания потеряла интерес к SPARC, доставшейся ей при покупке Sun, так что эпоха этой архитектуры подходит к концу.  Инвестиции были произведены ещё в апреле текущего года. За сумму в примерно 40 млн долларов было приобретено около 20 % акций Ampere Computing, за счёт чего Oracle получила одно из кресел в совете директоров. Кроме того, самой Ampere управляет Рене Джеймс (Renée James), которая также занимает место в совете директоров Oracle. Помимо инвестиций Oracle заплатила Ampere около $419 000 за разработку и тестирование оборудования в 2019 финансовом году. Интересно, что сама компания об инвестициях Oracle не сообщала, отметив лишь финансирование со стороны ARM Holdings и Carlyle Group. Ampere специализируется на разработке процессоров для облачных систем и серверов, которые сочетают высокую производительность и энергоэффективность.  В то же время Oracle всё меньше внимания уделяет собственной архитектуре SPARC и разработке процессоров на её основе. Заявлений об отказе от этой архитектуры пока что не последовало. Однако в отчёте за 2019 финансовый год Сафра Кац (Safra Catz), один из генеральных директоров Oracle, заявила: «Наши высокодоходные облачные решения Fusion и NetSuite быстро растут, и мы сокращаем свой низкорентабельный бизнес устаревшего [legacy] аппаратного обеспечения». В последний раз обе компании обновляли свои SPARC-процессоры в 2017 году. После выхода M8 Oracle фактически разогнала отдел, занимавшийся разработкой CPU. Fujitsu же после выпуска SPARC64 XII говорила о намерениях выпустить следующее поколение SPARC64 в 2020 году. Формально Fujitsu остаётся последним разработчиком высокопроизводительных SPARC-процессоров серверного уровня, но у компании наверняка немало ресурсов уходит на суперкомпьютер Post-K и ARM-процессор A64FX. И несмотря на то, что лицензиями на SPARC обладает довольно много компаний, среди которых есть и отечественные разработчики, вряд ли хоть кто-то из них будет вкладываться в серьёзное развитие архитектуры.  Наконец, хотелось бы отметить, что и операционная система Solaris 11, возможно, станет последней ОС от Oracle для платформы SPARC. Первый релиз вышел 8 лет назад, и хотя Oracle постепенно вносит в неё некоторые улучшения, признаки разработки Solaris 12 отсутствуют. А на днях компания заявила, что обеспечит стандартную поддержку системы Solaris 11 до 2031 года и расширенную поддержку до 2034 года. Таким образом, Oracle исполнит свои долгосрочные обязательства по обновлению Solaris. Однако будет крайне удивительно, если мы когда-либо увидим Solaris 12.

22.09.2019 [21:27], Андрей Созинов

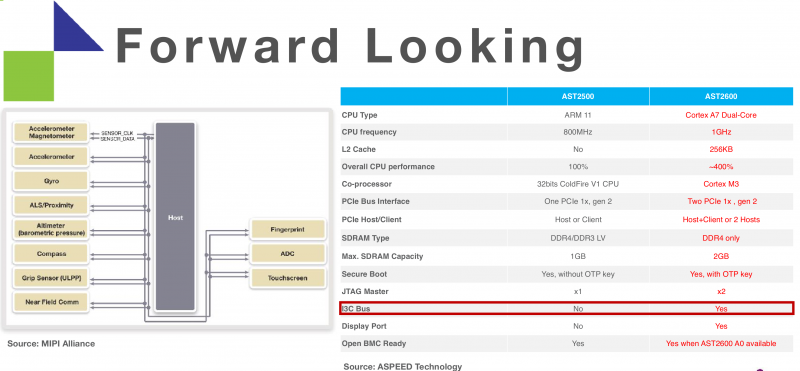

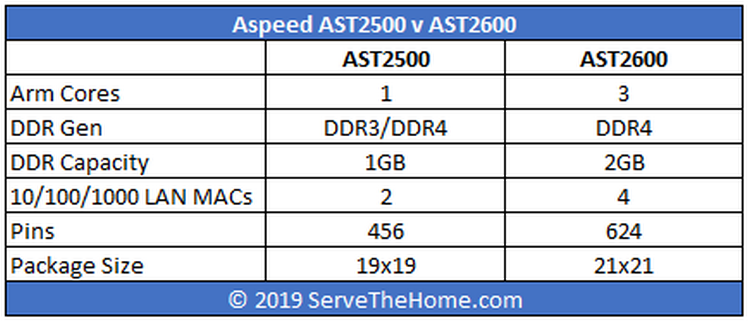

3 ядра, 2 гига: Aspeed выпустила BMC AST2600Компания Aspeed официально представила новый BMC под названием AST2600, который придёт на смену актуальному контроллеру AST2500. Новинка найдёт применение в серверах следующего поколения, которые появятся в 2020 году.  Предварительные данные о харакеристиках новинки, про которые мы уже писали, подтвердились. В основе 28-нм SoC Aspeed AST2600 лежат три ядра с архитектурой ARM: два основных Cortex A7 и одно вспомогательное Cortex M3. Контроллер позволяет использовать до 2 Гбайт RAM DDR4. BMC поддерживает технологии TrustZone и Secure Boot, которые призваны повысить безопасность. Также он обладает поддержкой до четырёх гигабитных сетевых интерфейсов. Обычно, правда, используется не более одного интерфейса, который нужен для подключения к BMC. Однако дополнительные сетевые порты можно использовать, например, для мониторинга и других задач.  Дополнительные возможности отразились на числе контактов — их теперь 624, что на 37 % больше по сравнению с предшественником — и, что важнее, на площади чипа, которая увеличилась до 441 мм 2. Соответственно, на материнской плате придётся отводить под BMC больше места.

23.02.2019 [20:20], Геннадий Детинич

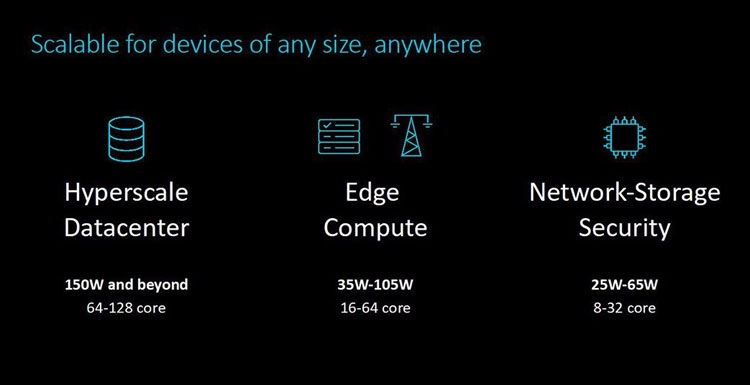

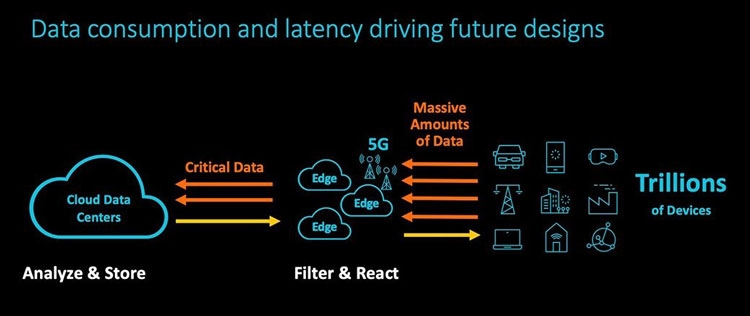

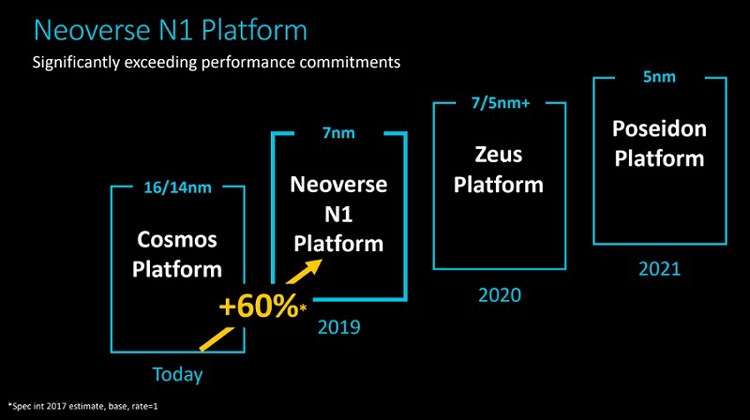

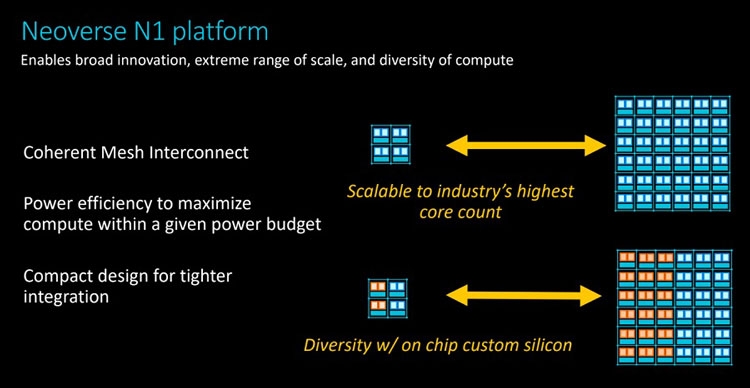

Анонс серверных платформ ARM Neoverse E1 и N1: шах и мат, IntelУж извините за столь кричащий заголовок, но ARM давно мечтает сказать нечто подобное в отношении серверных платформ Intel. Пока получается не очень. Как говорят в самой ARM, не вышло с первого раза, попробуем во второй. Не получится во второй раз, на третий точно всё будет как надо. А сейчас и повод-то отличный! Разработчики оригинальных ядер ARM из одноимённой компании ударили сразу с двух направлений: по масштабируемым сетевым платформам (Neoverse E1) и по масштабируемым серверным (Neoverse N1). Очевидно, что пока «мата» в этой партии явно не будет. Intel крепко держится за серверные платформы и одновременно тянет руки к периферийным как в виде распределённых вычислительных ресурсов в составе базовых станций, так и в виде обычных периферийных ЦОД. Тем не менее, шансы объявить Intel «шах» у ARM определённо есть.  Рассчитанную на несколько лет вперёд стратегию Neoverse компания ARM представила в середине октября прошлого года. Она предполагает три крупных этапа, в ходе которых будут выходить доступные для широкого лицензирования 64-битные ядра ARM Ares (7 нм), Zeus (7 и 5 нм) и Poseidon (5 нм). Планируется, что каждый год производительность решений будет возрастать на 30 %. Сама компания ARM, напомним, не выпускает процессоры и SoC, а лишь продаёт лицензии на ядра и архитектуру, которые клиенты компании обустраивают нужными им контроллерами и интерфейсами. У ARM настолько многочисленная армия клиентов, что она ожидает буквально цунами из сотен и тысяч миллиардов ядер в год уже в недалёком будущем. Когда-нибудь в этот водоворот ядер будут вовлечены и серверные платформы, а затем количество перейдёт в качество.  Разработка и анонс ядер Neoverse N1 ― это явление народу 7-нм ядер Ares. Процессоры могут нести от 4 до 128 ядер, объединённых согласованной ячеистой сетью. Платформа N1 может служить периферийным компьютером с 8-ядерным процессором с потреблением менее 20 Вт, а может стать сервером в ЦОД на 128-ядерных процессорах с потреблением до 200 Вт. Степень масштабируемости должна впечатлять. Кроме этого, как сообщают в ARM, производительность ядер N1 на облачных нагрузках в 2,5 раза выше, чем у 16-нм ядер предыдущего поколения Cosmos (Cortex-A72, A75 и A53). Кстати, прошлой осенью на платформе Cosmos компания Amazon представила фирменный процессор Graviton.  Производительность N1 при обработке целочисленных значений оказывается на 60 % больше, чем на ядрах Cortex-A72 Cosmos. При этом энергоэффективность ядер N1 также на 30 % выше, чем у ядер Cortex-A72. Как поясняют разработчики, платформа Neoverse N1 построена на «таких инфраструктурных расширениях, как виртуализация серверного класса, современная поддержка сервисов удалённого доступа, управление питанием и производительностью и профилями системного уровня».  Когерентная ячеистая сеть (Coherent Mesh Network, CMN), о которой выше уже говорилось, разработана с учётом высокого соответствия вычислительным возможностям ядер. По словам ARM, сеть обменивается с ядрами такой служебной информацией, которая позволяет устанавливать объём загрузки в память данных для упреждающей выборки, распределяет кеш между ядрами и определяет, как он может быть использован, а также делает много других вещей, которые способствуют оптимизации вычислений. Интересно отметить, что в составе процессоров на платформе Neoverse N1 может быть существенно больше 128 ядер, но с оптимальной работой возникнут проблемы. Точнее, вычислительная производительность упрётся в пропускную способность памяти. Так, ARM рекомендует для CPU с числом ядер от 64 до 96 использовать 8-канальный контроллер DDR4, а для 96–128 ядерных версий ― контроллер памяти DDR5. Платформа Neoverse E1 ― это решение для сетевых шлюзов, коммутаторов и сетевых узлов, которое, например, облегчит переход от сетей 4G к сетям 5G с их возросшей требовательностью к каналам передачи данных. Так, Neoverse E1 обещает рост пропускной способности в 2,7 раза, увеличение эффективности при передаче данных в 2,4 раза, а также более чем 2-кратный рост вычислительной мощности по сравнению с предыдущими платформами (ядрами). С масштабируемостью ядер E1 тоже всё в порядке, они позволят создать решение как для базовых станций начального уровня с потреблением менее 35 Вт, так и маршрутизатор с пропускной способностью в сотни гигабайт в секунду. Что же, ARM расставила на доске новые фигуры. Будет интересно узнать, кто же начнёт игру?

22.08.2018 [13:00], Геннадий Детинич

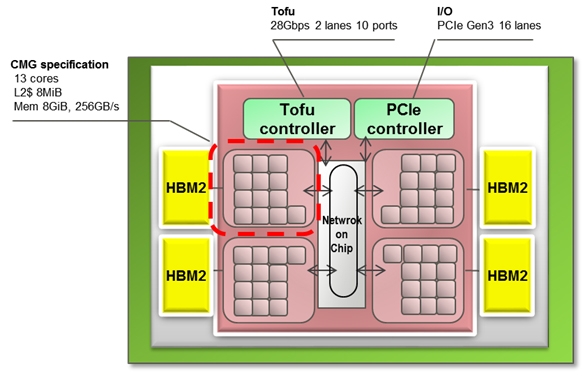

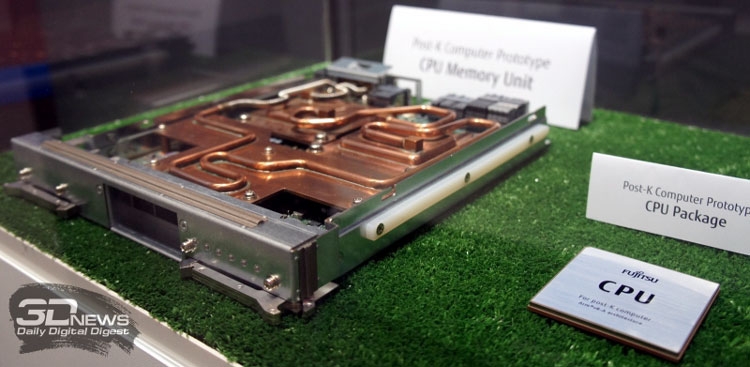

Раскрыты спецификации ARM-процессоров Fujitsu A64FX для суперкомпьютера Post-KПримерно через три года начнётся коммерческая эксплуатация суперкомпьютера Post-K, который компании Fujitsu и RIKEN разрабатывают на смену предыдущей совместной системы суперкомпьютера K (начал работать в 2011 году). Новая система Post-K обещает 100-кратно поднять производительность на уровне приложений. И сделано это будет благодаря переходу Fujitsu на ARM-совместимые ядра и новую архитектуру с масштабируемыми векторными инструкциями (Scalable Vector Extensions).  На прошедшей на днях конференции Hot Chips 30 (2018) компания Fujitsu впервые обнародовала спецификации новых процессоров, которые получили обозначение A64FX. Ни «A», ни «64», ни «FX» не имеют отношение к компании AMD, хотя в названии новых суперпроцессоров Fujitsu что-то немного согревает душу. Это процессоры с поддержкой 64-разрядных команд ARM и векторных инструкций длиной до 512 бит. Каждый процессор Fujitsu A64FX будет нести 48 вычислительных ядер и 4 вспомогательных ядра, разделённые на четыре блока, соединённых внутренней кольцевой шиной. Для связи с другими процессорами Fujitsu использует две линии внешнего интерфейса Tofu с пропускной способностью 28 Гбит/с. Строение процессора и внешний скоростной интерфейс обещают значительное наращивание параллелизма в вычислениях.

Fujitsu Каждый из 13-ядерных блоков поддержан кеш-памятью L2 объёмом 8 Мбайт. Кроме этого каждый из блоков напрямую обращается к модулю стековой памяти HBM2 объёмом 8 Гбайт. Суммарный объём памяти HBM2 у каждого процессора насчитывает 32 Гбайт, а общая скорость доступа достигает 1024 Гбайт/с. Поскольку память HBM2 можно рассматривать в качестве кеш-памяти третьего уровня, все или большинство операций выполняются в процессоре, что обещает отличный прирост производительности.  Процессор Fujitsu A64FX выпускается с использованием 7-нм техпроцесса, очевидно, что на линиях компании TSMC. Он насчитывает 8,7 млрд транзисторов. Пиковая производительность процессора для операций с двойной точностью достигает 2,7 терафлопс. Процессор без потерь на переход может вычислять операции с одинарной точностью и половинной, соответственно, в два и четыре раза быстрее. Также, за что надо благодарить тему машинного обучения, процессор A64FX оптимизирован для обработки 16- и 8-битных целочисленных значений.

09.11.2017 [13:07], Сергей Карасёв

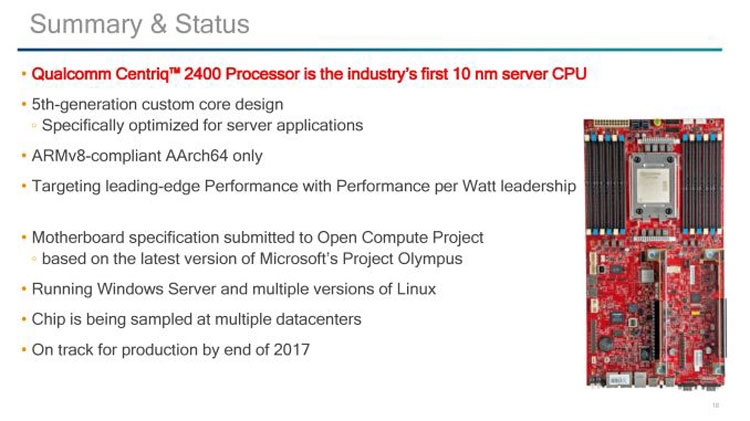

Начались коммерческие поставки 10-нм серверных чипов Qualcomm Centriq 2400Компания Qualcomm Datacenter Technologies, подразделение Qualcomm Incorporated, объявила о старте коммерческих поставок первых в мире 10-нанометровых серверных процессоров — решений семейства Centriq 2400. О разработке чипов Centriq 2400 стало известно ещё в декабре прошлого года. Позднее Qualcomm раскрыла детали об этих изделиях. И вот теперь настало время массовых поставок процессоров.

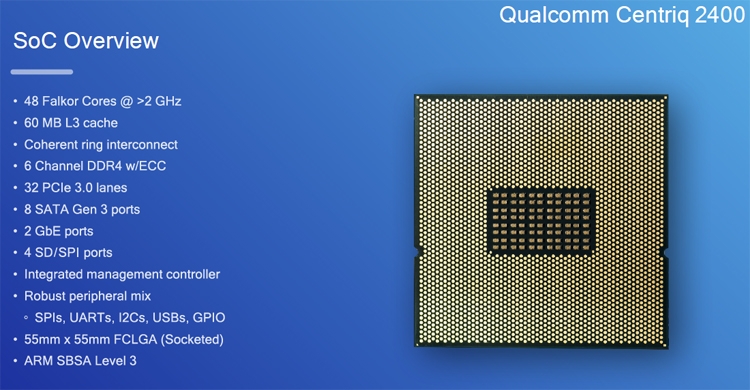

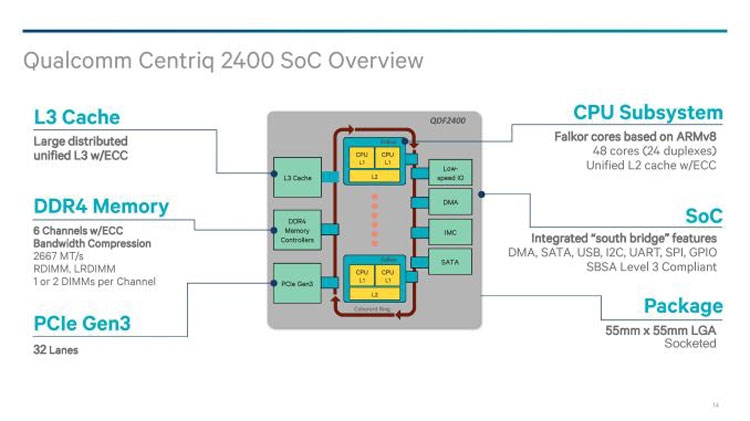

Источник изображений: Qualcomm В основу Centriq 2400 положены 64-битные вычислительные ядра с кодовым именем Falkor, обладающие поддержкой команд ARMv8. Количество таких ядер в составе чипов может достигать 48. Максимальная тактовая частота — 2,6 ГГц.  При изготовлении изделий применяется 10-нанометровая технология Samsung FinFET. Процессоры насчитывают до 18 млрд транзисторов. Каждая пара ядер снабжена 512 Кбайт общей кеш-памяти L2, а объём кеша L3 у чипов достигает 60 Мбайт.  В состав Centriq 2400 вошли 6-канальный контроллер памяти с поддержкой DDR4-2667 МГц ECC (до двух модулей на канал), 32 линии PCI Express 3.0, интерфейсы SATA, USB и пр.  Процессоры ориентированы на современные облачные платформы и центры обработки данных. Более подробную информацию о технических характеристиках можно найти здесь. Что касается стоимости, то изделие Qualcomm Centriq 2460, насчитывающее 48 вычислительных ядер, обойдётся заказчикам в 1995 долларов США.

02.11.2017 [12:12], Алексей Степин

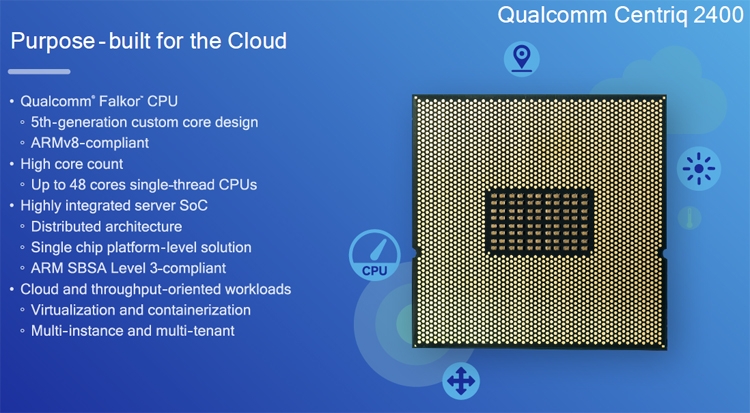

Qualcomm готовит почву для серверного процессора CentriqКомпанию Qualcomm представлять не надо — множество смартфонов оснащены именно процессорами этого разработчика, и многие пользователи не без оснований считают их лучшими, ставя данную серию выше моделей Samsung Exynos или MediaTek. С другой стороны, архитектура ARM пусть и очень медленно, но всё же проникает на корпоративный рынок, а именно — в сектор серверных решений. Известны проекты таких компаний, как Cavium, Applied Micro и даже AMD. Не стоит удивляться тому, что Qualcomm, имея огромный опыт в разработке процессоров с архитектурой ARM, тоже решила откусить кусочек от готовящегося пирога. Уже в течение двух лет существуют слухи о серверном процессоре Qualcomm, но теперь эти слухи переходят в разряд фактов. Последние несколько месяцев представители компании довольно охотно рассказывали о новом процессоре класса SoC под названием Centriq 2400.

Шестиканальный контроллер памяти обещает отсутствие нехватки ПСП Так, теперь известно, что этот чип будет производиться с использованием 10-нанометрового техпроцесса, и главной целевой аудиторией этого продукта станут поставщики облачных услуг и владельцы крупных ЦОД, для которых очень важную роль играют такие параметры, как энергопотребление и энергоэффективность процессоров. Замах Qualcomm взяла серьезный: если верить заявлениям, система на базе одного процессора Centriq сможет предложить уровень производительности, эквивалентный решениям на базе пары процессоров Xeon с архитектурой Skylake. В отличие от Intel, Qualcomm не обязана тянуть за собой тяжкое наследие совместимости с процессорами настольного класса и использует в своей разработке всё лучшее, что было воплощено в чипах для смартфонов и планшетов. Centriq 2400 должен получить 24 процессорных ядра с кодовым названием Falkor. Это архитектура собственной разработки Qualcomm, но отвечающая всем требованиям стандарта ARMv8.

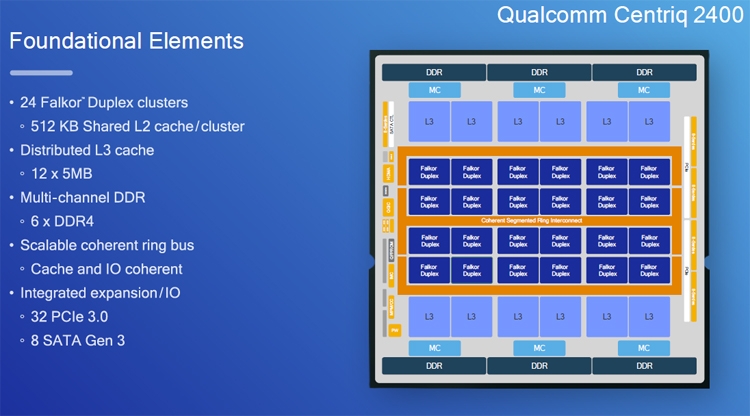

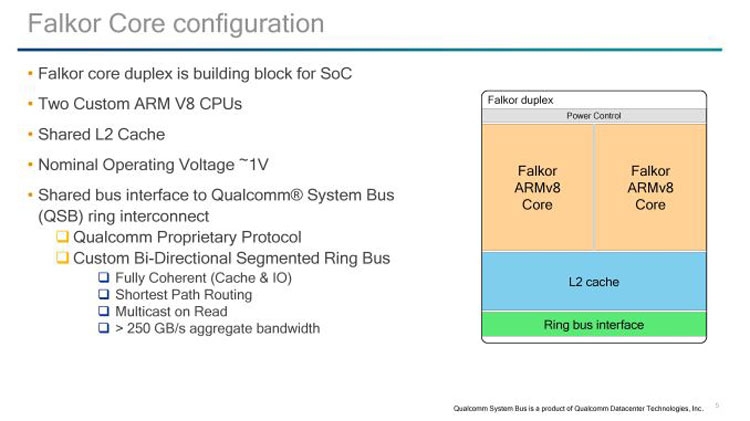

Выглядит Cenriq практически так же, как и обычные Xeon, Opteron или EPYC На диаграмме слово Duplex присутствует не зря, поскольку в целом можно говорить о 48 однопоточных ядрах, но в будущем компания планирует наращивать и количество ядер, и количество потоков на ядро. Интересен также тот факт, что Intel отказалась от кольцевой внутренней шины в новых Xeon, а Qualcomm, наоборот, пришла к этой идее. Контроллер памяти DDR4 у Centriq шестиканальный и дополненный, к тому же, средствами аппаратного сжатия данных. Имеется встроенная поддержка сетевых стандартов 10 и 100 GbE, 32 линии PCIe (скорее всего, 3.0) и функций южного моста, а также развитая подсистема управлением питанием. В рамках Open Compute Project компания уже разработала две референсные платформы формата 1OU — с одним либо с двумя процессорными разъёмами под Centriq. Пока это практически всё, что известно о Сentriq 2400. Кое-что было опубликовано нами ранее, но пока мы не знаем тактовых частот и сроков начала массовых поставок. Однако судя по имеющимся сведениям, Qualcomm решила заняться развитием серверной ветки ARM всерьёз и надолго.

23.08.2017 [12:40], Геннадий Детинич

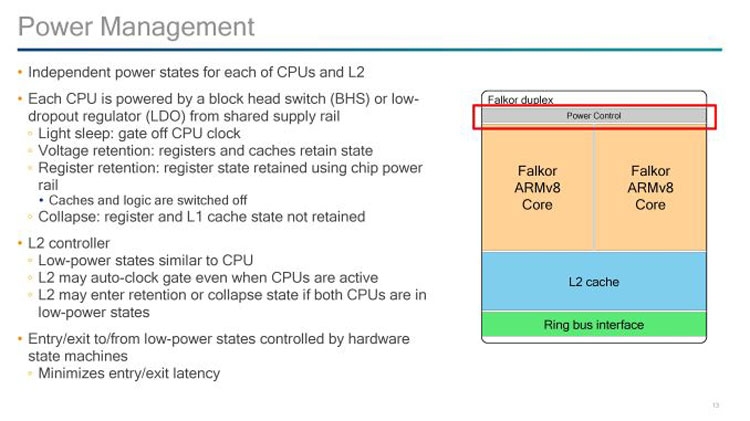

Qualcomm поделилась деталями о 48-ядерных процессорах Centriq 2400Пять лет назад компания Qualcomm приступила к разработкам процессора для серверного рынка. Успешный разработчик уникальных вычислительных архитектур, совместимых с наборами команд ARM, вполне обоснованно решил перенести опыт создания SoC для смартфонов и планшетов в область высокопроизводительных серверных решений. К тому времени требования к серверным процессорам изменились в сторону снижения потребления и лучшей масштабируемости. Социальные сети и облачные сервисы создают настолько неравномерную нагрузку на вычислительные ресурсы ЦОД, что обычные x86-совместимые или RISC/UNIX-платформы перестают считаться эффективным инструментом для решения насущных задач.  В декабре 2016 года Qualcomm сообщила о завершении разработки и начале пробных поставок процессора Centriq 2400 с числом ядер до 48 штук. На днях компания подтвердила график вывода новинки на рынок, который предусматривает массовые коммерческие поставки SoC Centriq 2400 позднее в текущем году. Также Qualcomm поделилась деталями о строении и архитектуре Centriq 2400. Ниже мы расскажем о ключевых особенностях разработки.  Начнём с того, что внутренний согласованный интерфейс однокристальной сборки Centriq 2400 представляет собой сегментированную кольцевую шину. Компания Intel, как нам известно, в новых серверных и высокопроизводительных настольных процессорах перестанет использовать кольцевую шину в пользу ячеистой шины, что должно улучшить масштабируемость архитектуры для многоядерного окружения. Компания AMD использует другой принцип обмена данными между кластерами в процессорах на ядрах Zen. Все они соединены между собой двунаправленной шиной, топология которой ближе к кольцевой. Сегментированная кольцевая шина в составе Centriq 2400 использует преимущества кольцевой шины (простота, сравнительно низкое потребление) и элементы ячеистой сети внутри сегмента, что даёт возможность балансировать между скоростью, задержками и потреблением.  Вычислительные ядра в составе Centriq 2400 самостоятельно разработаны инженерами компании и носят кодовое имя Falkor. Это 64-битные решения с поддержкой команд ARMv8, которые разбиты на модули из двух связанных ядер (дуплексное строение, по определению Qualcomm). Подобное строение позволяет выпускать SoC Centriq 2400 с заданным числом ядер и облегчает масштабирование вычислительной структуры в процессе выполнения задачи. Каждая пара ядер имеет разделяемую кеш-память L2 и разделяемый доступ к кольцевой шине Qualcomm System Bus (QSB).  Для снижения потребления каждое ядро и кеш-память L2 имеют ряд состояний потребления энергии, которые контролируются на аппаратном уровне и могут переключаться с минимальными задержками. Вычислительные конвейеры Falkor имеют переменную длину с внеочередным исполнением команд. Это снижает вероятность простоя конвейеров в процессе работы с командами и инструкциями, не оптимизированными для немедленного исполнения.  Иерархия кеш-памяти Falkor оптимизирована для обработки значительных массивов данных. Так, кеш-память первого уровня для приёма данных объёмом 32 Кбайт дополнена «несимметричной» кеш-памятью L1 для инструкций: 24 Кбайт L0 и 64 Кбайт L1 (всего 88 Кбайт). Всё это снабжено многоуровневым движком предварительной выборки, который динамически адаптируется под текущую нагрузку. В состав SoC Centriq 2400 вошли 6-канальный контроллер памяти с поддержкой DDR4-2667 МГц ECC (до двух модулей на канал), 32 линии PCI Express 3.0, интерфейсы SATA, USB и более специализированные сигнальные структуры. Также Centriq 2400 несёт интегрированный криптографический блок TrustZone и поддерживает аппаратную виртуализацию. В компании Qualcomm уверены, что данную разработку ждёт успешное будущее. |

|